Project Snapshot

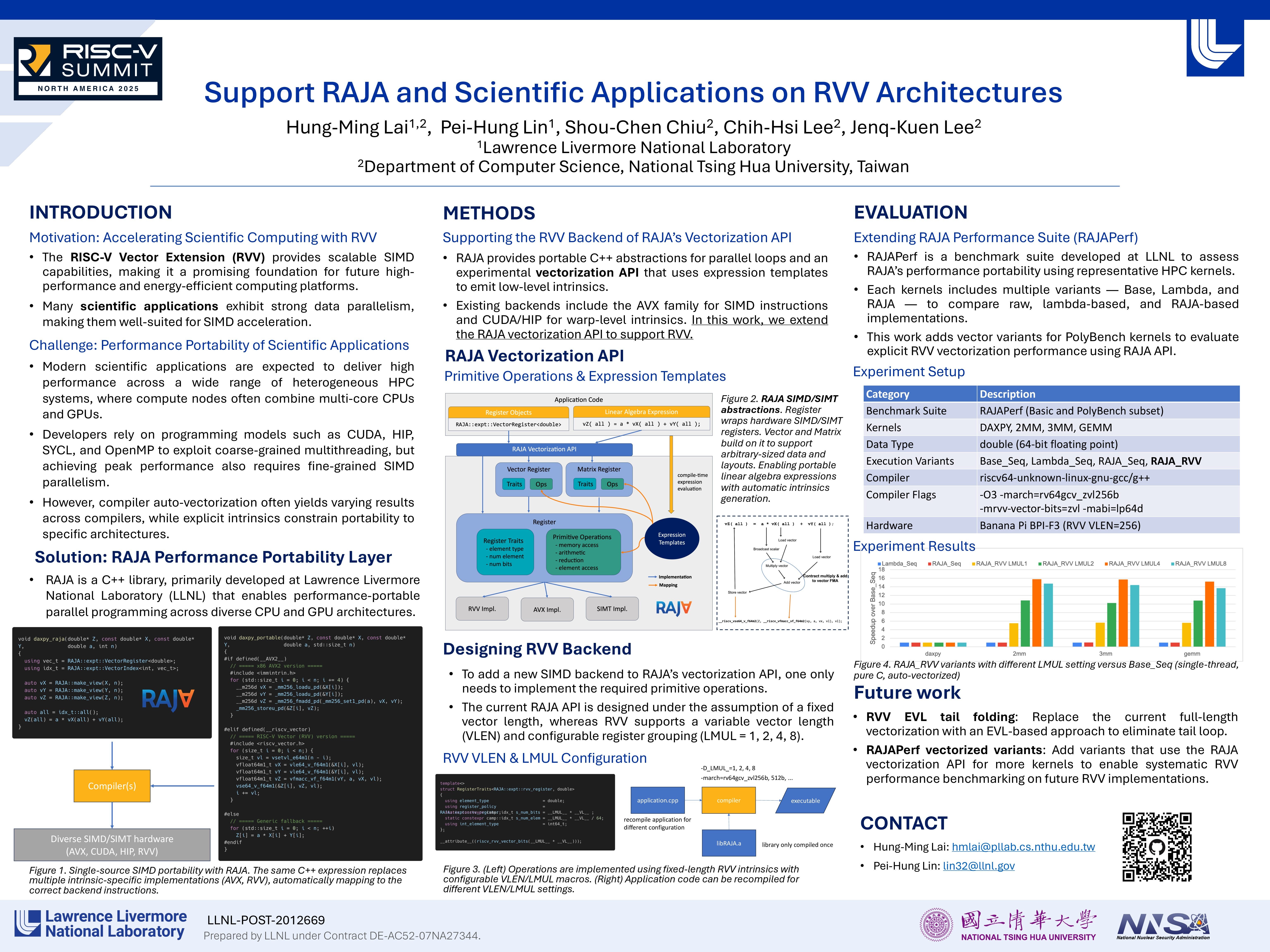

In this work, we aim to make RVV more accessible to scientific applications by integrating it into the RAJA performance-portability framework. RAJA is a C++ library primarily developed at Lawrence Livermore National Laboratory that offers loop-based abstractions and multiple execution backends to deliver portable performance across heterogeneous systems. We contribute a new RVV backend to RAJA’s vectorization API, enabling RVV-aware optimizations within RAJA-based applications.

In Their Own Words

Poster Preview

Meet the Authors

Hung-Ming Lai

PhD Student in Computer Science at National Tsing Hua University in Taiwan

Hung-Ming is a PhD student in the Department of Computer Science, National Tsing-Hua University, Taiwan. His thesis advisor is Prof. Jenq-Kuen Lee. His research interests are in compiler optimizations on RISC-V with SIMD computations, AI compiler optimizations, and compiler analysis for program reliability.

Pei-Hung Lin

Computer Scientist at Lawrence Livermore National Laboratory in the USA

Dr. Pei-Hung Lin is a computer scientist in the Center for Applied Scientific Computing (CASC) at Lawrence Livermore National Laboratory (LLNL). His research expertise spans compiler optimizations, parallel programming models, and the integration of machine learning techniques into high-performance computing (HPC) workflows. He received his Ph.D. in Computer Science from the University of Minnesota.

Shou-Chen Chiu

Master’s Student in Computer Science at National Tsing Hua University in Taiwan

Shou-Chen is a graduate student in the Department of Computer Science at National Tsing Hua University, advised by Prof. Jenq-Kuen Lee. His research interests are in compiler optimization on RVV and AI compiler optimization.

Chih-Hsi Lee

Master’s Student in Computer Science at National Tsing Hua University in Taiwan

Chih-Hsi is a master’s student in the Department of Computer Science, National Tsing-Hua University, Taiwan. His advisor is Prof. Jenq-Kuen Lee. His research focuses on register optimizations for RVV and compiler optimizations on RISC-V.

Jenq-Kuen Lee

Professor at National Tsing Hua University in Taiwan

Jenq‑Kuen Lee is a Professor of Computer Science at National Tsing Hua University, Taiwan, specializing in optimizing compilers. He co‑authored Auto‑tuning Fixed‑point Precision with TVM on RISC‑V Packed SIMD (ACM TODAES 2023) and TVM Hybrid‑OP Optimization on RISC‑V SIMD (IEEE Access 2024). His team enhanced SIMDe to automate ARM NEON‑to‑RVV. He presented the RISC‑V ISA for sub‑FP8 at RISC‑V Summit 2024 and maintained contributions across the RISC‑V GitHub ecosystems and TVM upstream on RVV.