Project Snapshot

How does performance modeling accelerate real hardware innovation in open RISC-V designs?

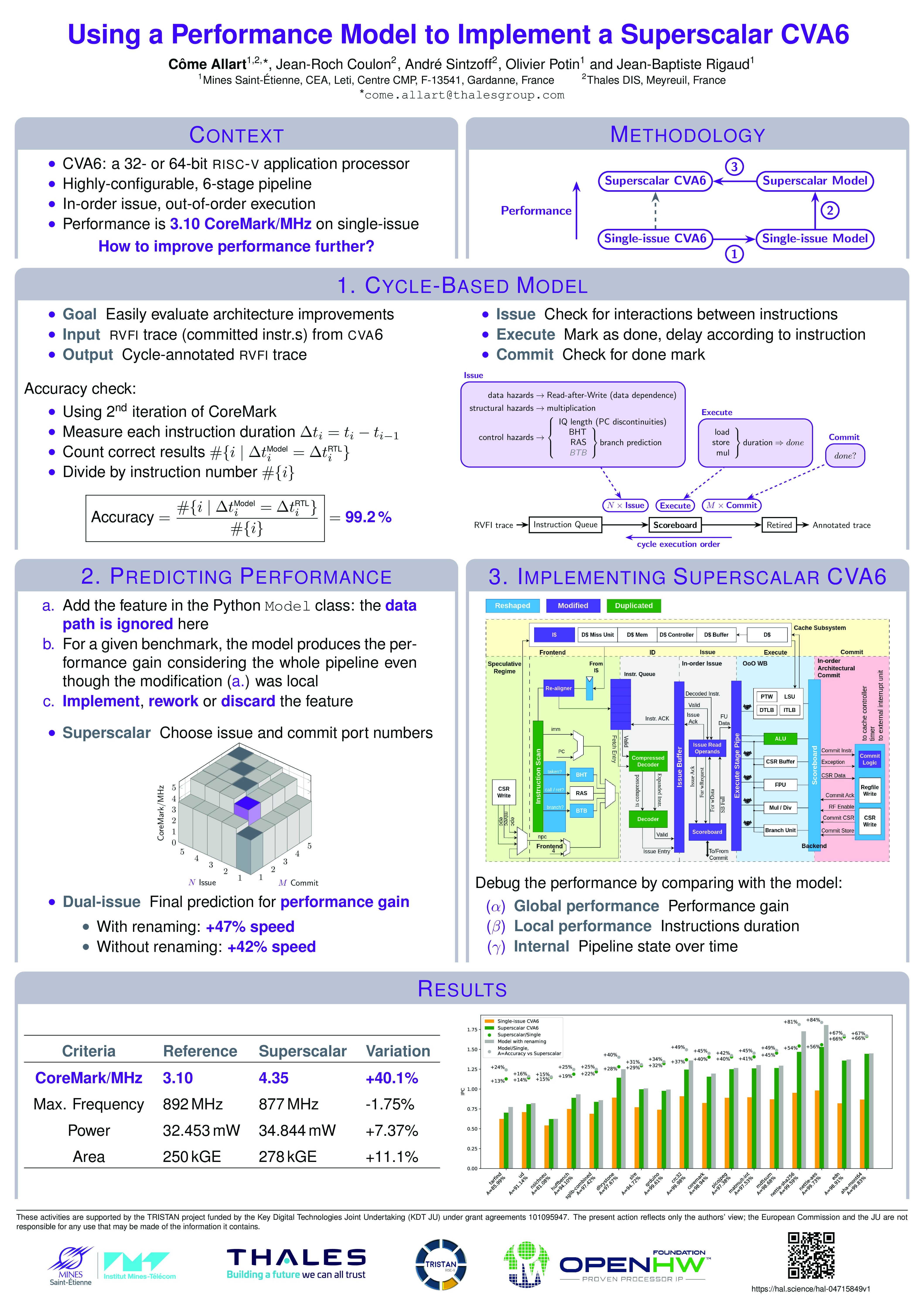

In this paper, Thales demonstrates a performance model of the CVA6 RISC-V processor, built to evaluate performance-related modifications before implementing them in RTL.

By creating a precise cycle-based Python model (99.2% accuracy on Coremark) to detect and fix performance bugs, they guided the implementation of a dual-issue CVA6 core.

The result: +40% higher CoreMark/MHz performance with only a small power (+7%) and area (+11%) increase.

In Their Own Words

Poster Preview

Meet the Authors

Côme Allart

PhD student in Computer Science and Microprocessor Design at Thales DIS and Mines Saint-Étienne, CEA, Leti, Centre CMP in France

Côme Allart is a PhD student at Thales DIS and Mines Saint-Étienne. His research focuses on improvements of the performance of CVA6, generally for generic applications and more specifically for PQC-related applications.

Jean-Roch Coulon

Processor architect at Thales DIS in France

Jean Roch Coulon is RISC-V Architect at Thales group in France, he designed processors to add security in ARM, SPARC, proprietary and now RISC-V implementations. Expert in processor, toolchain, security, cryptography or code size density. His main contributions in RISC-V are the 32bits version of CVA6 (CV32A6), CV-X-IF and verification. He is an OpenHW group committer; developing, reviewing and merging CVA6 and CORE-V-VERIF pull requests.

André Sintzoff

Engineer at Thales DIS in France

André Sintzoff is a senior engineer at Thales and currently the verification leader for CV32A60X core at Thales DIS France. He received his MSc in microelectronics from UCLouvain, Belgium. He has worked in industry for several positions related to embedded software (3G modems, smartcards). Since 2019, he is working on open source RISC-V processors.

Olivier Potin

Associate professor at Mines Saint-Étienne, CEA, Leti, Centre CMP in France

Olivier Potin holds a MBA and a PhD in Microelectronics. He started his career as a software engineer. Then he was co-founder and technical manager of Oridao developing cryptographic embedded RFID solutions before turning to research in test domain at LIRMM. In 2014, he joined the École des Mines de Saint-Étienne as Associate Professor in the department of Secured Architectures and Systems (SAS).

He is involved in several collaborative research projects on securing software execution on the RISC-V processor against hardware attacks with academic/industrial partners in France. As project coordinator (SCREAM, COFFI) or scientific WP leader (AIMMUNITY, COGITO) for Mines Saint-Etienne, Olivier Potin was designed and evaluated HW/SW protection schemes to secure integrated circuits.

Olivier Potin takes part of the ISMIN program committee, actively teaches microelectronic courses during the all three years of ISMIN degree.

Jean-Baptiste Rigaud

Full-time Professor at Mines Saint-Étienne, CEA, Leti, Centre CMP at Thales DIS in France

Jean-Baptiste Rigaud, age 50, received his PhD in Microelectronics in December 2002 in the National Polytechnic Institute of Grenoble, within TIMA Laboratory. He was named associate professor at Mines Saint-Etienne graduate school of engineering in September 2003. He is based in the Microelectronics Centre of Provence within the mixed team /CEA-LETI.

His research activities focus on the design of robust integrated circuits against fault or side channel attacks. It concerns the design flow as well as the design of specific countermeasures or the improvement of security characterization technics.

He has co-supervised 20 PhDs including 5 currently as supervisor. He has been involved in about fifteen collaborative projects. He was the technical leader of the ANR MISTRAL project. Today he is professor at Mines Saint-Etienne

Mike Thompson

Director of Verification at OpenHW Foundation in Canada

Mike Thompson a senior IC functional verification engineer and engineering manager who has led both large and small teams in all aspects of the discipline including simulation, emulation, prototyping and formal verification. He has both hands-on and management level experience and is a strong proponent of coverage-driven verification efforts. Since 2019 Mike has been Director of Engineering for the Verification Task Group at the OpenHW Foundation and has led simulation and formal verification efforts for multiple RISC-V cores in the OpenHW CORE-V family.