Project Snapshot

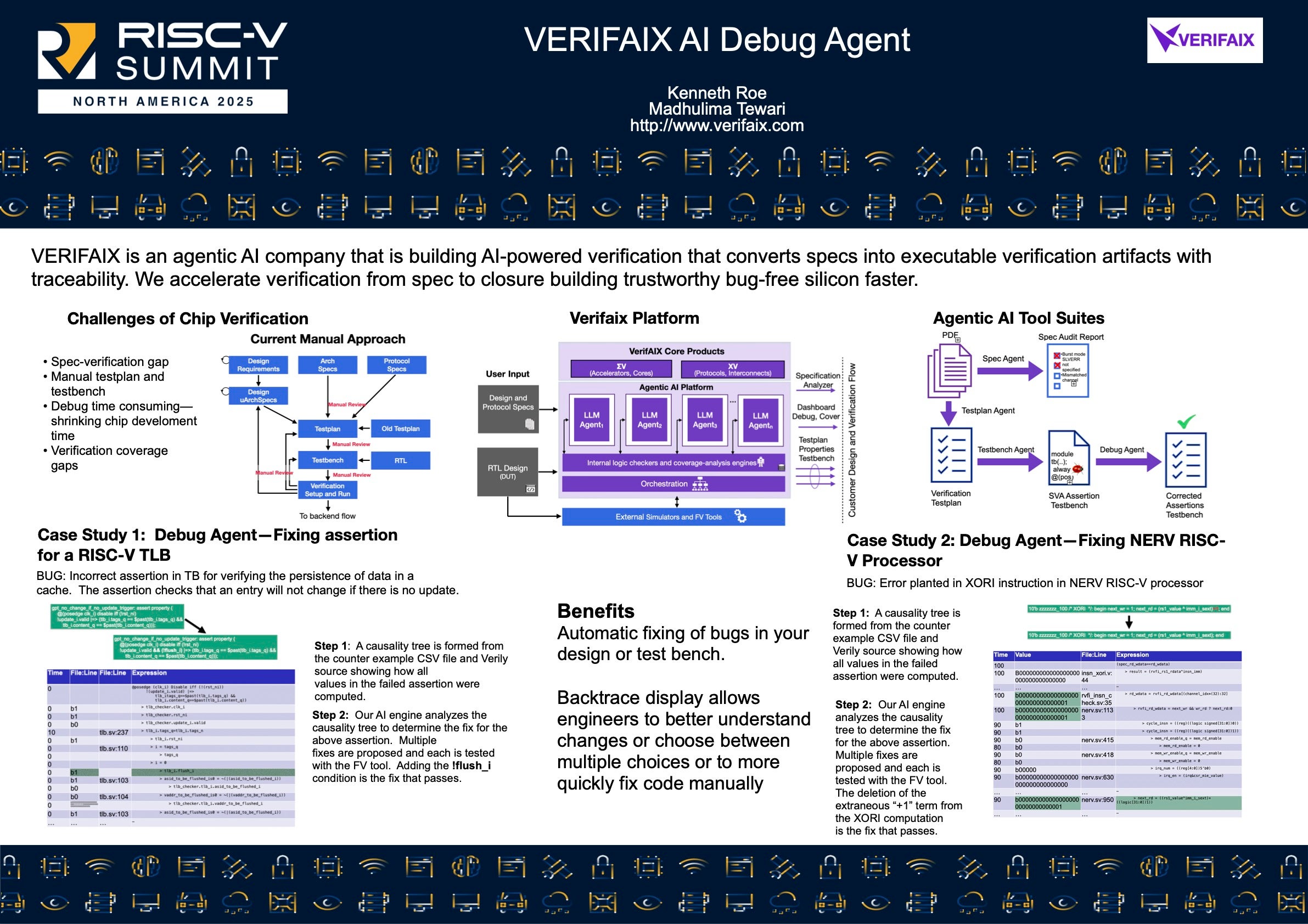

This poster will explore AI-driven techniques for automatically fixing verification failures. Maintaining regression suites is one of the most resource-intensive tasks in hardware verification—small RTL changes can trigger thousands of test failures, each requiring manual analysis and repair. We introduce the Verifaix Debug Agent, a tool that automates root cause analysis and fixes regression failures.

One of the most significant bottlenecks in hardware verification is debugging failures in large regression suites. As RTL designs evolve, even minor changes can trigger failures across thousands of tests. Maintaining these regressions is a labor-intensive process—especially in large-scale projects like GPUs or server-class CPUs, where dedicated teams are often required just to keep regression suites operational.

We introduce the Verifaix Debug Agent, an AI-powered tool that automates the root cause analysis and resolution of regression failures. When a test fails, the Debug Agent determines whether the issue lies in the design or the test itself, applies a fix, and re-executes the test to ensure correctness without side effects.

In Their Own Words

Poster Preview

Meet the Authors

Kenneth Roe

Chief Architect, Verifaix, USA

Kenneth Roe has decades of experience in the semiconductor industry, having held key roles at companies such as SiFive, Synopsys, and Intel. He has led both formal verification teams and the development of advanced verification tools. Ken holds a Ph.D. in Formal Verification from Johns Hopkins University and possesses deep expertise in the inner workings of formal verification technologies.

Madhulima Tewari

Founder and CEO, Verifaix, USA

Madhulima Tewari is a seasoned entrepreneur and tech leader with deep expertise in AI, EDA, and systems. She led product development at startups acquired by Ericsson, Oracle, and IBM, and has been a teaching staff for NLP/AI courses at Stanford. She built sign-off tools at Synopsys and led verification for complex SoCs at NXP and Sun. She now focuses on applying AI to transform chip design verification.