Week In Review: Design, Low Power | Jessee Allen, Semiconductor Engineering

Standards

CHIPS Alliance and RISC-V International will work jointly to update the OmniXtend Cache Coherency specification. The two groups formed a new OmniXtend... Read more.

DARPA adds RISC-V to its Toolbox: Defense researchers can get special access to SiFive chip designs | Katyanna Quach

Engineers and scientists working on American military research programs can now access RISC-V processor core designs and associated blueprints through DARPA's Toolbox,... Read more.

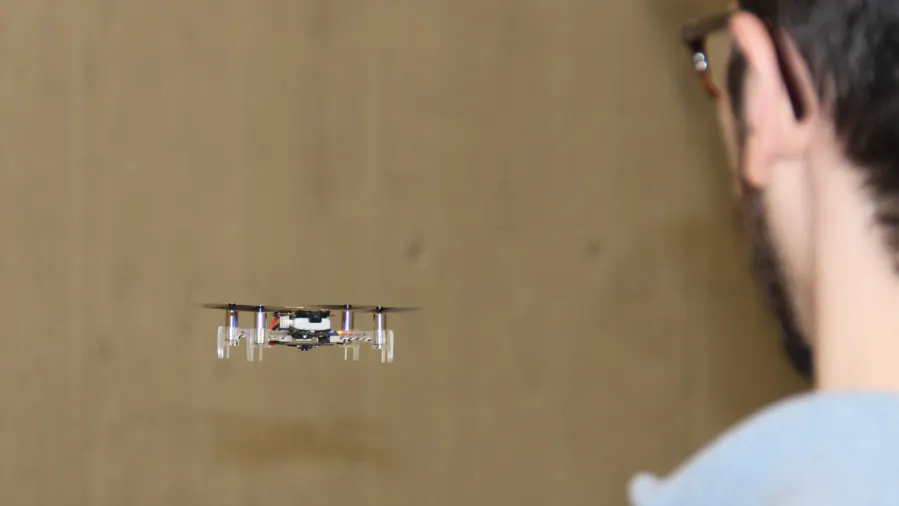

An Ultra-Low Power RISC-V Chip and a Clever Neural Network Give This Crazyflie “Top-Notch” Autonomy | Gareth Halfacree

GAP8 "Parallel Ultra-Low Power" chip draws just 86mW to drive a 135 frames-per-second autonomous flight system with pose estimation.

Read the full article.... Read more.

RISC-V Extension Boasts Dramatic Improvements in Ultra-Low Power IoT Wireless Signal Processing | Gareth Halfacree

Extensions to the open source ISA offer "substantial energy savings" for common IoT protocols including LoRa and Bluetooth Low Energy.

Read the full article.... Read more.

Axiomise Unveils Formal Verification 101 Training Program | GlobeNewsWire

LONDON, April 06, 2021 (GLOBE NEWSWIRE) -- Axiomise, the leading provider of cutting-edge formal verification consulting, training, services, and IP, today unveiled... Read more.

Axiomise Unveils Formal Verification 101 Training Program | Press Release

Certification-Based Self-Paced On-Demand Continuing Education Program Includes Best Practices for Using Formal Verification

LONDON, April 06, 2021 (GLOBE NEWSWIRE)... Read more.

Video: #CSWSpring21 / RISC-V for acceleration of data-parallel workloads: from IoT to HPC

In this talk by Luca Benini (University of Bologna / ETH Zurich), we will look into RISC-V based architectures for acceleration of data-parallel workloads. The focus... Read more.

First Google-Sponsored MPW Shuttle Launched at SkyWater with 40 Open Source Community Submitted Designs | Press Release

Collaboration among SkyWater, Efabless and Google enables industry’s first open source ASICs

BLOOMINGTON, Minn. & SAN JOSE, Calif.--(BUSINESS WIRE)--SkyWater... Read more.

Video: ECC3118-1: Lab on RISC-V Emulator

ECC3118-1: MIKROPEMPROSES (MICROPROCESSOR)... Read more.

ARM vs RISC-V Vector Extensions | Erik Engheim

A comparison of the RISC-V vector extension (RVV) and ARM scalable vector extension (SVE/SVE2).

Read the blog.... Read more.