We recently held our fall 2021 CHIPS Alliance workshop with nearly 160 attendees present for informative seminars covering a range of topics including porting Android…

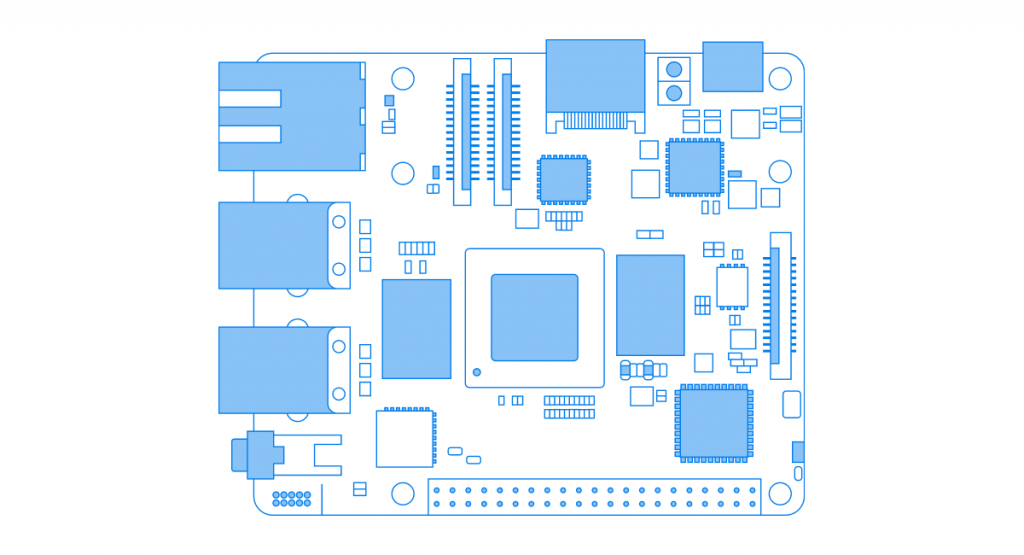

Kit Close-Up: Lattice Semiconductor’s Crosslink-NX Development Kit | William G. Wong, Electronic Design

Kit Close-Up: Lattice Semiconductor’s Crosslink-NX Development Kit | William G. Wong, Electronic DesignEditor Bill Wong examines the board and the software tools available for FPGA development. It supports a range of soft core processors including RISC-V. The…

Socionext, Techsor and ZiFiSense Unveil IC for “ZETag,” a New Cloud Tag to Utilize ZETA Communication | AI Technology Insights

Socionext, Techsor and ZiFiSense Unveil IC for “ZETag,” a New Cloud Tag to Utilize ZETA Communication | AI Technology InsightsSocionext Inc., ZiFiSense and Techsor announced that the companies have jointly developed a new IC “SC1330,” designed for ZETag, a next generation Cloud Tag that…

Intel CTO Greg Lavender interview — Why chip maker is spending on both manufacturing and software | Dean Takahashi, Venture Beat

Intel CTO Greg Lavender interview — Why chip maker is spending on both manufacturing and software | Dean Takahashi, Venture BeatIntel has been on a spending spree ever since Pat Gelsinger returned to the company as CEO earlier this year. He pledged to spend $20…

Vortex is an open source Hardware and Software project to support GPGPU based on RISC-V ISA extensions. Currently Vortex supports OpenCL/CUDA and it runs on…

My experience installing Libero SoC in Ubuntu and Windows 10 | Jean-Luc Aufranc, CNX Software

My experience installing Libero SoC in Ubuntu and Windows 10 | Jean-Luc Aufranc, CNX SoftwareA few weeks ago, I received Microchip PolarFire SoC FPGA Icicle Kit with FPGA fabric and hard RISC-V cores capable of handling Linux. I wrote…

GCC 12 Merges Initial Support For RISC-V’s Bitmanip Extensions | Michael Larabel, Phoronix

GCC 12 Merges Initial Support For RISC-V’s Bitmanip Extensions | Michael Larabel, PhoronixFollowing the recent RISC-V Bitmanip work in Binutils, the GCC 12 compiler has now landed preliminary support for the RISC-V ISA's bit manipulation extension. RISC-V's…

SiFive has become, thanks to the RISC-V architecture, one of the most promising companies in the semiconductor world. We are not talking about a newcomer,…

Alibaba Cloud pushes into South Korea, Thailand with faster, more efficient data centers | Peter Cohen, RCR Wireless News

Alibaba Cloud pushes into South Korea, Thailand with faster, more efficient data centers | Peter Cohen, RCR Wireless NewsAlibaba Cloud has announced plans to open new regional data centers in South Korea and Thailand. New server hardware from Alibaba Cloud improve data center…

IAR Systems Extends Functional Safety Offering for RISC-V with Build Tools for Linux | Tiera Oliver, Embedded Computing Design

IAR Systems Extends Functional Safety Offering for RISC-V with Build Tools for Linux | Tiera Oliver, Embedded Computing DesignIAR Systems announced that its build tools for RISC-V supporting deployment in Linux-based frameworks have been certified by TÜV SÜD for functional safety development. The…

Allwinner D1s/F133 RISC-V processor integrates 64MB DDR2 | Jean-Luc Aufranc, CNX Software

Allwinner D1s/F133 RISC-V processor integrates 64MB DDR2 | Jean-Luc Aufranc, CNX SoftwareAllwinner D1s (aka F133) is a cost-down version of Allwinner D1 RISC-V processor introduced earlier this year together with a Linux capable development board, with…

IAR Build Tools for Linux for RISC-V now certified as a qualified tool for safety-related embedded development Uppsala, Sweden—October 25, 2021—IAR Systems®, the future-proof supplier…

This video explains the RTL architecture of an RV32I RISC-V processor. Also, it shows how we can create the RISC-V RTL using basic building blocks…

Run Linux on BeagleV Starlight in Renode | Antmicro

Run Linux on BeagleV Starlight in Renode | AntmicroBeagleV Starlight is an upcoming affordable general-purpose Linux-capable RISC-V platform, and as such understandably generates a lot of interest in the development community. It is currently…

Unboxing, review and getting started with BeagleV, the first affordable RISC-V computer designed to run Linux. The video demonstrates Fedora image booted on BeagleV beta…

Nulcei Studio provides a free integrated development for the GigaDevice RISC-V microcontroller family. This video shows you how to get started with the product using…

PicoCom tapes out multicore RISC-V OpenRAN chip for ORANIC board | eeNews Europe, Nick Flaherty

PicoCom tapes out multicore RISC-V OpenRAN chip for ORANIC board | eeNews Europe, Nick FlahertyUK chip designer PicoCom is taping out its core chip for OpenRAN wireless networks and developed a board-level product called ORANIC to speed up deployment.…

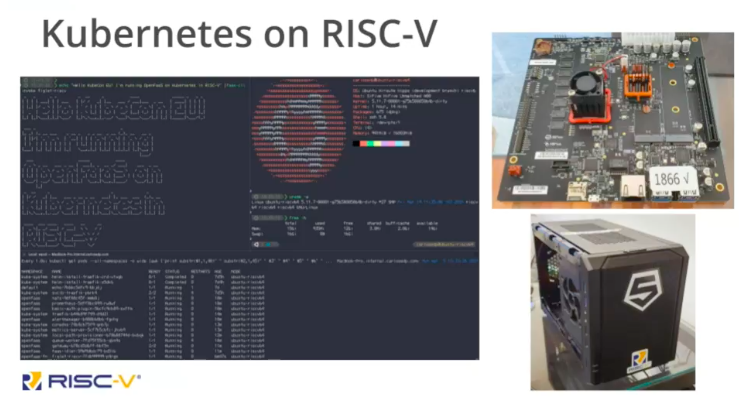

Don’t miss out! Join us at our upcoming event: KubeCon + CloudNativeCon North America 2021 in Los Angeles, CA from October 12-15. Learn more at…

Recently, Antmicro announced the release of its ARV module that integrates a RISC-V-based SoC and other supporting components. So what is RISC-V, what features does…

What is RISC-V and Why is it Important? | ICS, Jeff Tranter

What is RISC-V and Why is it Important? | ICS, Jeff TranterWhen it comes to processor architectures, you're probably familiar with x86 and ARM, but have you ever heard of RISC-V? If not, you owe it…

How does RISC-V fit into automotive systems? | EE World, Jeff Shepard

How does RISC-V fit into automotive systems? | EE World, Jeff ShepardRISC-V is being used in a surprising range of automotive systems ranging from ASIL-D safety rated controllers and security co-processors, artificial intelligence (AI) accelerators, controllers…

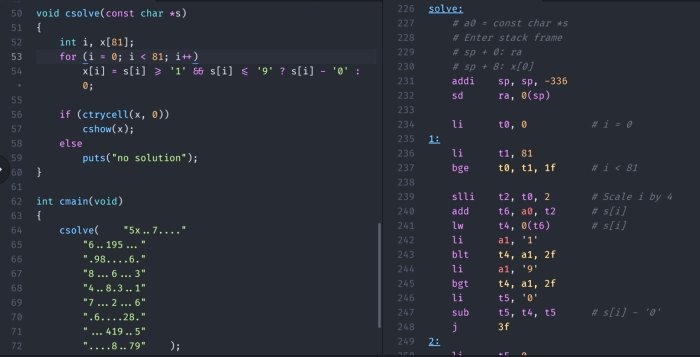

Five tips for writing RISC-V assembly code #RISCV | Stephen Marz

Five tips for writing RISC-V assembly code #RISCV | Stephen MarzWriting assembly is itself an art. When C, C++, or any other language is compiled, the compiler determines the art of writing assembly. However, this…

KubeCon EU: The Case for Bare Metal | B. Cameron Gain, The New StackKubern

KubeCon EU: The Case for Bare Metal | B. Cameron Gain, The New StackKubernThe great shift to the cloud has often “clouded” the critical role that on-premises infrastructure — and more specifically — bare metal servers can play…

Dialog Semiconductor Selected as SiFive Preferred Power Management Partner for RISC-V Development Platforms | Dialog Semiconductor

Dialog Semiconductor Selected as SiFive Preferred Power Management Partner for RISC-V Development Platforms | Dialog SemiconductorDialog’s highly efficient, cost effective PMICs, deliver “Exact Fit” power solutions London, United Kingdom – May 11, 2021 – Dialog Semiconductor plc (XETRA:DLG), a leading…