Chiplet Strategy is Key to Addressing Compute Density Challenges | Balaji Baktha, EE Times

Chiplet Strategy is Key to Addressing Compute Density Challenges | Balaji Baktha, EE TimesData center workloads are quickly evolving, demanding high compute density with varying mixes of compute, memory and IO capability. This is driving architectures that are…

RISC-V Mentorship: Formal Verification of SweRV EL2 Processor | Shashank V.M.

RISC-V Mentorship: Formal Verification of SweRV EL2 Processor | Shashank V.M.Background I was in the final year of my undergraduate degree in Electronics and Communication Engineering when I learnt out about the RISC-V Mentorship program from the RISC-V…

Intel backs RISC-V for Nios FPGA processor | Nick Flaherty, EE News Europe

Intel backs RISC-V for Nios FPGA processor | Nick Flaherty, EE News EuropeIntel's Nios V soft processor for its FPGAs uses the RISC-V: RV32IA architecture with atomic extensions, 5-stage pipeline and AXI4 interfaces. Intel has developed a…

Security Enclave IP based on RISC-V | Silex Insight

Security Enclave IP based on RISC-V | Silex InsightSee the latest brochure from Silex Insights on security enclave IP based on RISC-V. See the full brochure.

Startup Funding for September 2021 | Jesse Allen, Semiconductor Engineering

Startup Funding for September 2021 | Jesse Allen, Semiconductor EngineeringStartups focused on data center chips had a big month in September. A new emergent from stealth promises to accelerate big data analytics, and startups…

Sipeed Teases Linux-Capable 64-Bit RISC-V System-on-Module — for Under $20 | Gareth Halfacree, Hackster.io

Sipeed Teases Linux-Capable 64-Bit RISC-V System-on-Module — for Under $20 | Gareth Halfacree, Hackster.ioSipeed has released details on a new system-on-module board built around the RISC-V Allwinner D1 chip — and it's aiming to bring the Linux-capable device…

Initializing RISC-V: A Guided Tour for ARM Developers | Ahmad Fatoum and Rouven Czerwinski, Pengutronix

Initializing RISC-V: A Guided Tour for ARM Developers | Ahmad Fatoum and Rouven Czerwinski, PengutronixRISC-V is the hot and upcoming architecture in the embedded space. While a majority of embedded developers have earned their chops programming for ARM processors…

RISC-V is so much more than just an ISA for processors. Because of the openness of RISC-V, we are seeing an increase in innovation around…

CHERI Software Release for Summer 2021 | George Neville-Neil, Light Blue Touchpaper

CHERI Software Release for Summer 2021 | George Neville-Neil, Light Blue TouchpaperThe CHERI project at SRI International and the University of Cambridge are pleased to announce our second CHERI reference software-stack release. The release supports the…

SiPearl opens design centre in Grenoble, looks for 50 engineers | Nick Flaherty, EE News Europe

SiPearl opens design centre in Grenoble, looks for 50 engineers | Nick Flaherty, EE News EuropeSiPearl has opened a design centre in Grenoble with the goal of recruiting 50 engineers on the site by the end of 2022. The company…

Calculating the big picture: Future HPC efforts will soon see off its von Neumann past | Rupert Goodwins, The Register

Calculating the big picture: Future HPC efforts will soon see off its von Neumann past | Rupert Goodwins, The RegisterHigh-performance computing (HPC) has a very different dynamic to the mainstream. It enables classes of computation of strategic importance to nation states and their agencies,…

Abstract Extracting features from sensing data on edge devices is a challenging application for which deep neural networks (DNN) have shown promising results. Unfortunately, the…

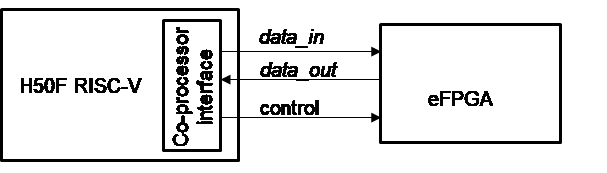

Using eFPGA core for CPU ISA extension, reconfigurability | IMEN BAILI, EDN

Using eFPGA core for CPU ISA extension, reconfigurability | IMEN BAILI, EDNProcessor extensibility with an external hardware module like FPGA or DSP core isn’t a new concept. However, there are no existing hardware solutions that allow…

CAES Gaisler Signs Contract with the European Space Agency for New Advanced Space Processor | Design & Reuse

CAES Gaisler Signs Contract with the European Space Agency for New Advanced Space Processor | Design & ReuseApril 20, 2021 -- Gothenburg, Sweden – CAES Gaisler, a leader in advanced mission-critical electronics, announced today that it has received a contract from the…

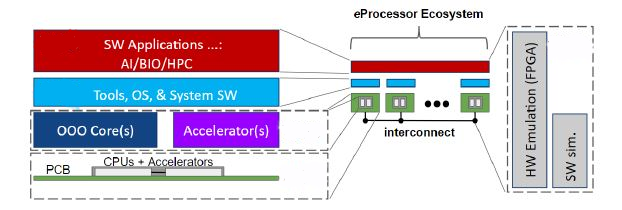

BSC Working Towards First Completely Open Source European Full-Stack Ecosystem Based on New RISC-V CPU | HPCWire

BSC Working Towards First Completely Open Source European Full-Stack Ecosystem Based on New RISC-V CPU | HPCWireApril 19, 2021 — BSC researchers lead eProcessor, a project that will create a 100% European out-of-order (OoO) RISC-V core to produce new embedded High…

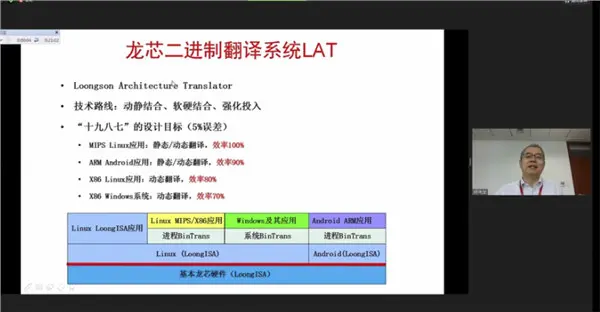

Loongson unveils LoongArch CPU instruction set architecture for processors made in China | JEAN-LUC AUFRANC, CNX Software

Loongson unveils LoongArch CPU instruction set architecture for processors made in China | JEAN-LUC AUFRANC, CNX SoftwareLoongson is a Chinese company better known for its MIPS processors, and we often see the company being mentioned in mainline Linux changelogs with regards to…

Pervasive computing — IoT, edge, cloud, data center, and back PC maker Dell Technologies is spinning off 81% equity ownership of VMWare to two standalone public companies. VMWare, founded in…

Silex Insight and Andes Technology Extend Strategic Partnership to Deliver Flexible and Scalable Root-of-Trust Security IP Solution | Electronics Engineering

Silex Insight and Andes Technology Extend Strategic Partnership to Deliver Flexible and Scalable Root-of-Trust Security IP Solution | Electronics EngineeringSilex Insight and Andes Technology extend strategic partnership to deliver flexible and scalable Root-of-Trust security IP solution Silex Insight and Andes Technology offer the eSecure…

In its continued effort to reduce reliance on foreign technologies (particularly U.S.-made), China has been mostly focusing on getting up to speed with the hardware…

AUSTIN, Texas, April 15, 2021 /PRNewswire/ -- Inspire Semiconductor, Inc. (InspireSemi™) announced today that two customers have placed pre-orders for its Gen2 compute accelerator solution for blockchain,…

Morpheus Turns a CPU Into a Rubik’s Cube to Defeat Hackers | Samuel K. Moore, IEEE Spectrum

Morpheus Turns a CPU Into a Rubik’s Cube to Defeat Hackers | Samuel K. Moore, IEEE SpectrumUniversity of Michigan’s Todd Austin explains how his team’s processor defeated every attack in DARPA's hardware hacking challenge Last summer, 580 cybersecurity researchers spent 13,000 hours trying…

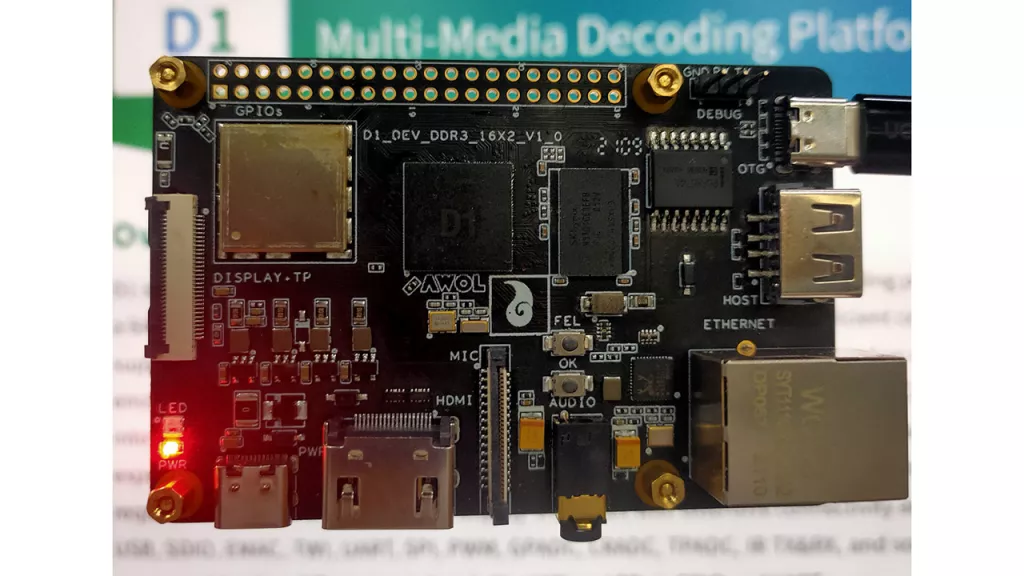

Allwinner’s RISC-V D1 Chip, Single-Board Computer Leak Ahead of Next Week’s Launch Announcement | Gareth Halfacree, hackster.io

Allwinner’s RISC-V D1 Chip, Single-Board Computer Leak Ahead of Next Week’s Launch Announcement | Gareth Halfacree, hackster.io64-bit XuanTie C906-based chip will drive a Raspberry Pi-alike single-board computer, with availability expected this May. Low-power processor specialist Allwinner is preparing to launch a…