See Danny Pratama's step-by-step tutorial for running SPIKE Simulator with Proxy Kernel. This tutorial assumes you already have compiler for RISC-V. Watch the full tutorial…

In this tutorial Danny Pratama will explain step by step how to use SPIKE internal debugger or with GDB using OpenOCD Watch the full tutorial…

In this tutorial Danny Pratama will explain the steps to compiling your own RISC-V GNU toolchain or use the prebuilt toolchain by SiFive Watch the…

Imperas Software Ltd.,a leader in virtual platforms and high-performance software simulation, today announced that SiFive, Inc., an industry leader in RISC-V processors and silicon solutions,…

Deep neural networks… IN SPAAACE: Vector-enhanced RISC-V chips could give satellites onboard AI | Gareth Halfacree, The Register

Deep neural networks… IN SPAAACE: Vector-enhanced RISC-V chips could give satellites onboard AI | Gareth Halfacree, The RegisterBoffins from the Delft University of Technology (TU Delft) and European Space Agency (ESA) have penned a paper detailing the design of a processor they…

New SiFive Performance Family of application processors offers best in class performance, area, and efficiency for a wide variety of markets SAN MATEO, Calif., June…

Co-simulating HDL has been possible in Renode since the 1.7.1 release, but the functionality - critical for hardware/software co-development as well as FPGA use cases…

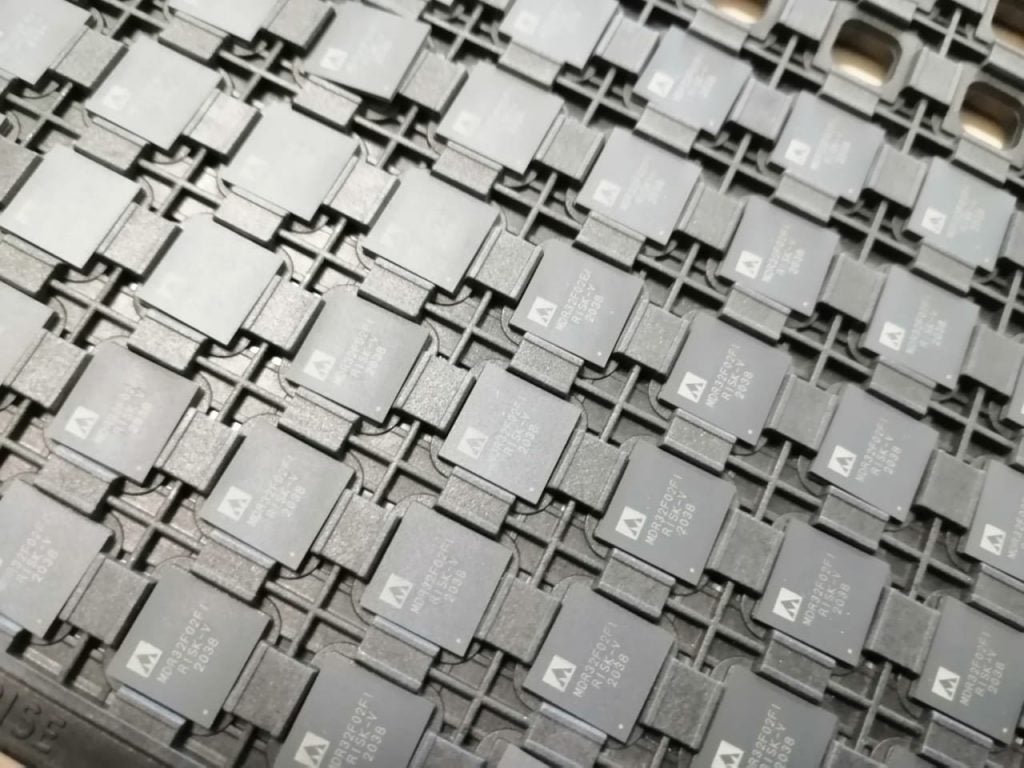

Overview This white paper describes how low-power memory technology, originally designed for large, high density, SRAMs has been enhanced and adapted to deliver low-power, low-voltage…

Read Daniel Mangum's blog series exploring RISC-V by breaking down real programs and explaining how they work. You can read the blog here. You can view…

Imperas Expands Partnership with Valtrix to Address Growing RISC-V Verification Market

Imperas Expands Partnership with Valtrix to Address Growing RISC-V Verification MarketImperas Software Ltd., the leader in RISC-V processor verification technology, today announced a multi-year distribution and support agreement with Valtrix Systems, provider of design verification products…

Video: SSRC Collaborates with Global Universities on RISC-V-Based Secure Flight Computer System | ATRC

Video: SSRC Collaborates with Global Universities on RISC-V-Based Secure Flight Computer System | ATRCTII’s Secure Systems Research Centre (SSRC) has partnered with global universities to develop a RISC-V-Based Secure Flight Computer System. SSRC is a strategic member of…

SiFive Deepens RISC-V Core Lineup | William G. Wong, Electronic Design

SiFive Deepens RISC-V Core Lineup | William G. Wong, Electronic DesignSiFive keeps cranking out new versions of its RISC-V cores. Its two most recent additions include the Performance P550 core and the Performance P270 vector…

Micro Magic details its 1GHz RISC-V processor | Peter Clarke, ee News Europe

Micro Magic details its 1GHz RISC-V processor | Peter Clarke, ee News EuropeeeNews Europe Mark Santoro, CEO of Micro Magic, said the processor core had also been designed so that it can operate down to at least 350mV,…

Linux 5.10 LTS release – Main changes, Arm, MIPS and RISC-V architectures | Jean-Luc Aufranc, CNX Software

Linux 5.10 LTS release – Main changes, Arm, MIPS and RISC-V architectures | Jean-Luc Aufranc, CNX Softwarehas just released Linux 5.10: Ok, here it is – 5.10 is tagged and pushed out. I pretty much always wish that the last week was…

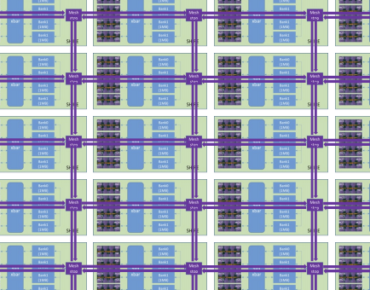

ET-SoC-1 Chip with More Than 1,000 RISC-V Cores Aimed at Accelerating Machine Learning | Abhishek Jadhav, hackster.io

ET-SoC-1 Chip with More Than 1,000 RISC-V Cores Aimed at Accelerating Machine Learning | Abhishek Jadhav, hackster.ioAt the RISC-V Summit 2020, Art Swift, CEO of Esperanto Technologies, announced the development of a chip based on the open source RISC-V architecture with…

Compiling a Benchmark for RISC-V | TechTechPotato

Compiling a Benchmark for RISC-V | TechTechPotatoWe've been after a compile benchmark for a while, something that was easy enough to run on multiple systems but also portable, could be automated,…

RISC-V Summit 2020 showcases a growing ecosystem and a wider application spectrum | Roberto Frazzoli, EDACafe'

RISC-V Summit 2020 showcases a growing ecosystem and a wider application spectrum | Roberto Frazzoli, EDACafe'here and here – commissioned by Mentor. In fact, 2020 has been a year of growth for this open instruction set architecture, as underlined by Calista Redmond, CEO…

Embedded Studio for RISC-V now comes with SEGGER Linker | Neil Tyler, New Electronics

Embedded Studio for RISC-V now comes with SEGGER Linker | Neil Tyler, New ElectronicsSEGGER’s Embedded Studio for RISC-V now comes with the SEGGER Linker in addition to the GNU linker. The SEGGER Linker has been developed from…

The Genius of RISC-V Microprocessors | Erik Engheim, Medium

The Genius of RISC-V Microprocessors | Erik Engheim, MediumSince the RISC and CISC wars that raged in the late 1990s, people have claimed that RISC and CISC doesn’t matter anymore. Many will claim…

Calista Redmond of RISC-V International Tells Us About Its Open-Source Development Model and COVID-19 | Kossi Adzo, startup.info

Calista Redmond of RISC-V International Tells Us About Its Open-Source Development Model and COVID-19 | Kossi Adzo, startup.infoFirst of all, how are you and your family doing in these COVID-19 times? Calista Redmond: We’re doing well, thank you. We’re fortunate to be keeping…

Linker Shrinks RISC-V Application Size | Nick Flaherty, eeNews Europe

Linker Shrinks RISC-V Application Size | Nick Flaherty, eeNews EuropeSegger is a custom Linker in addition to the GNU linker. This is based on the same code as the Segger Linker for ARM, adding integrated integrity check…

Seagate Announces Its Own RISC-V Cores for Future Storage Controllers | Joel Hruska, Extreme Tech

Seagate Announces Its Own RISC-V Cores for Future Storage Controllers | Joel Hruska, Extreme Techchips, which are not referred to by any codename or brand, come in two flavors: A high-performance core and an area-optimized core. The high performance core…