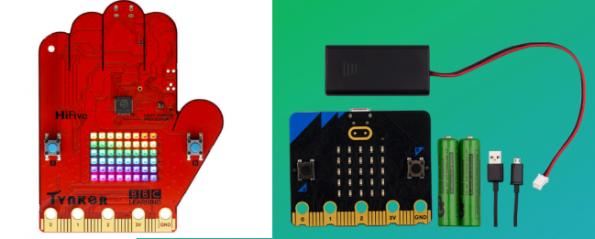

Connecting to the ISS crew manifest using an online API, the BBC HiFive and its onboard ESP32 using Micropython.

Experts at the Table: This is the last part of the series of articles derived from the DVCon panel that discussed Verification in the Era of…

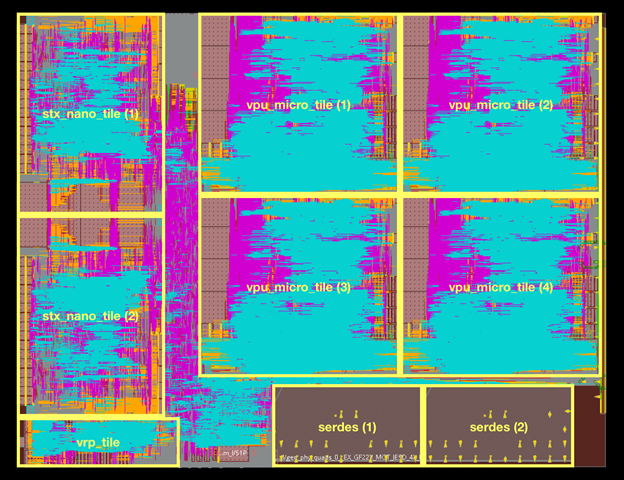

June 1, 2021 -- The European Processor Initiative (EPI) https://www.european-processor-initiative.eu/, a project with 28 partners from 10 European countries, with the goal of helping the EU achieve…

European Processor Initiative Announces EPAC1.0 RISC-V Test Chip Taped-out | HPCWire

European Processor Initiative Announces EPAC1.0 RISC-V Test Chip Taped-out | HPCWireJune 1, 2021 — The European Processor Initiative (EPI), a project with 28 partners from 10 European countries, with the goal of helping the EU…

*RISC-V 32-bit Instruction Type Decode logic design in 120sec* Just imagine what all things you can do in RISC-V MYTH 5-day workshop. Many participants have…

Keynote Session: Hypervisor Extensions in RISC-V - Robert Eshleman, Vates SAS This talk presents the virtualization capabilities offered by the RISC-V Hypervisor ISA extension (H…

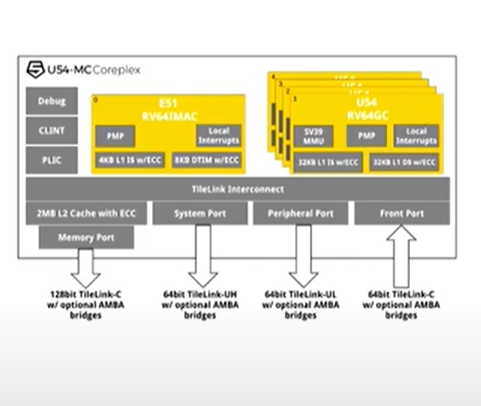

SEGGER’s emRun Runtime Library Licensed by SiFive for Superior Code Size and Performance Improvements | Design & Reuse

SEGGER’s emRun Runtime Library Licensed by SiFive for Superior Code Size and Performance Improvements | Design & ReuseMonheim am Rhein, Germany – May 31, 2021 -- The SEGGER emRun runtime library is available as part of the recently announced SiFive 21G1 release. SiFive’s…

首届RISC-V中国峰会(RISC-V World Conference China)将于6月21日在上海科技大学盛大开幕。本次峰会预计线下超过1000人、线上超过10000人参会,超过100家厂商进行演讲或参展,将会成为国内迄今为止规模最大的以RISC-V为主题的峰会。峰会期间将会有共计19场Workshop及Tutorials同地举办,组织方涵盖了国内外知名RISC-V厂商、研究机构及国内高校、开源技术组织。目前所有同地举办活动的举办时间和地点已经确定,详细议程将由各个活动的组织方在近期发布,请关注RISC-V中国峰会的官网( https://www.riscv-conf-china.com )和微信公众号(CNRV)获取后续议程更新。 时间 同地活动 6月21日(周一)下午 芯来科技赋能本土RISC-V生态 芯来科技 6月21日(周一)下午 RISC-V技术与生态研讨会(RVTE2021) 中科院软件所 6月22日(周二)下午 RISC-V新型计算架构和应用驱动的数据存储和管理 组织单位:上海科技大学 6月23日(周三)下午 RVfpga: 基于RISC-V的完整计算机体系结构课程 Imagination 6月24日(周四)上午 RISC-V Total…

Are we seeing the takeover from RISC-V? | Electropages, Robin Mitchell

Are we seeing the takeover from RISC-V? | Electropages, Robin MitchellThe RISC-V architecture, which is in direct competition with ARM, is making more news headlines recently. So how do RISC-V and ARM differ, what products…

Alibaba is making its cloud OS compatible with multiple chip architectures | TechCrunch, Rita Liao

Alibaba is making its cloud OS compatible with multiple chip architectures | TechCrunch, Rita LiaoAlibaba’s cloud computing unit is making its Apsara operating system compatible with processors based on Arm, x86, RISC-V, among other architectures, the company announced at a conference on…

The growth of RISC-V is built on the collaborative efforts of the individuals and organizations in the technical community. Our continued progress relies on the…

中国上海,2021年5月27日 – 首届RISC-V中国峰会(RISC-V World Conference China)将于6月21日在上海科技大学盛大开幕。本次峰会预计线下超过1000人、线上超过10000人参会,超过100家厂商进行演讲或参展,将会成为国内迄今为止规模最大的以RISC-V为主题的峰会。这也是RISC-V第一次在北美以外地区举办同等规模的峰会。其中主会将举办三天半(6月22日至25日上午),同期将举办各类同地活动,包括技术研讨会(workshops)、RISC-V厂商技术推广(tutorials)等,并设置厂商展区(booth)供产品及服务展示、合作洽谈。 本次峰会由上海科技大学和中国科学院软件研究所联合主办,中国RISC-V产业联盟(CRVIC)、中国开放指令生态联盟(CRVA)、CNRV社区协办,广州市智能软件产业研究院承办。本次峰会的举办得到了RISC-V国际基金会的大力支持。峰会期间的活动亮点包括: 6月22日 – 倪光南院士等学术界、产业界大咖带来开幕主题演讲,从生态、开源、产业等大格局着眼推动RISC-V发展的重要意义。 6月21日-26日 – 由国内外企业、研究机构、开发者、科研工作者为带来多场技术报告、研讨会、圆桌论坛和技术推广。主题涵盖:RISC-V 的新产品发布、技术路线介绍、面向RISC-V的软件支持、RISC-V在各类业务领域的应用生态、芯片行业的格局及趋势等。 本届RISC-V中国峰会的大会主席、RISC-V国际基金会董事会成员、中科院计算所副所长包云岗教授表示:“本次峰会旨在为产业界和学术界提供交流、合作、创新的平台,全面推动RISC-V在中国及全球的发展,推广RISC-V产业领域创新技术产品,推动RISC-V的科研及教学,助力产业人才的培养。” 芯来科技创始人兼CEO胡振波表示:“期待在RISC-V中国峰会与产学研各界一起深度思考RISC-V在本土的应用发展。峰会开幕日正值芯来科技成立三周年之际,我们将把三年来在本土推动RISC-V落地的进程和取得的成绩与与会者分享。同时,芯来科技也将在本次峰会上发布新的标志性内核产品,新的IP普惠计划,以及新的开源教学平台,敬请关注。” 北京希姆计算将在大会发布第一代可编程的、基于RISC-V指令集的NerualScale神经网络计算加速架构,并展示第一款面向云端AI推理计算的通用可编程NPU芯片——P920。创始人詹荣开表示:“希姆计算的P920 NPU芯片凭借基于RISC-V的自研NerualScale架构,在计算的能效比与可编程性两个方面都达到非常高的先进水平,将以更低的成本给云端客户带来成倍的算力密度提升。” RISC-V 嵌入式处理器解决方案供货商Andes 将于本次大会中展示各项研发产品亮点,在硬件方面包括高效能64位的RISC-V向量处理器NX27V升级至最新版本RVV0.10和增加高带宽平行处理的配置,以及最高达4核的超纯量多核应用处理器A45MP/AX45MP。在软件方面将带来 AndeSight IDE v5.0加速AI和IoT应用程序开发;COPILOT 5.4透过ACE给予NX27V高效能的Streaming…

Read the full article. ]]>

already available. As usual, the new release introduces a range of features, modifications and fixes, enabling developers to design complex embedded IoT systems more effectively…

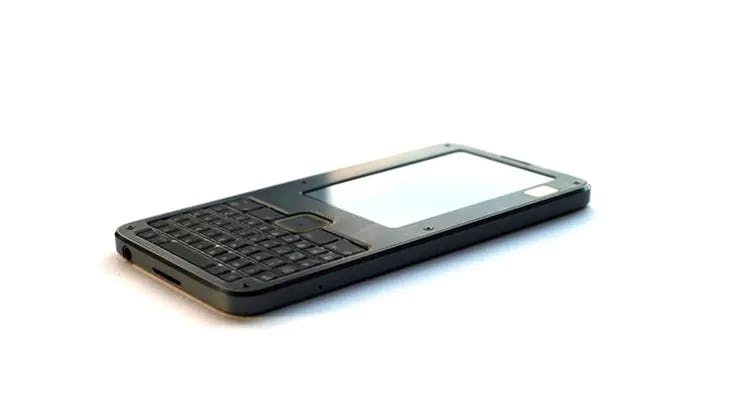

'Bunnie' Huang Dives Deep Into the Security of the RISC-V-Powered Precursor | Gareth Halfacree, hackster.io

'Bunnie' Huang Dives Deep Into the Security of the RISC-V-Powered Precursor | Gareth Halfacree, hackster.ioBuilt around an FPGA, the Precursor is not only massively hackable but also built with security in mind — and can be potted for protection.…

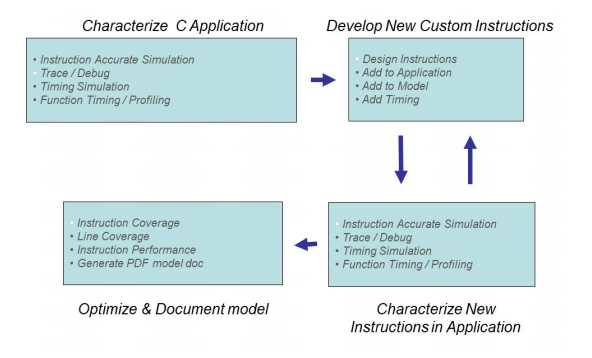

Imperas RISCV Custom Instruction Flow Application Note (Whitepaper) | Imperas

Imperas RISCV Custom Instruction Flow Application Note (Whitepaper) | ImperasRead Full Whitepaper]]>

Battle of the BBC boards | Nick Flaherty, eeNews Europe

Battle of the BBC boards | Nick Flaherty, eeNews EuropeSiFive on the board and coding lessons narrated by Thirteenth Doctor, Jodie Whittaker. The ‘hand-shaped’ board uses the FE310-G003 from SiFive that is based around the E-31 RISC-V…

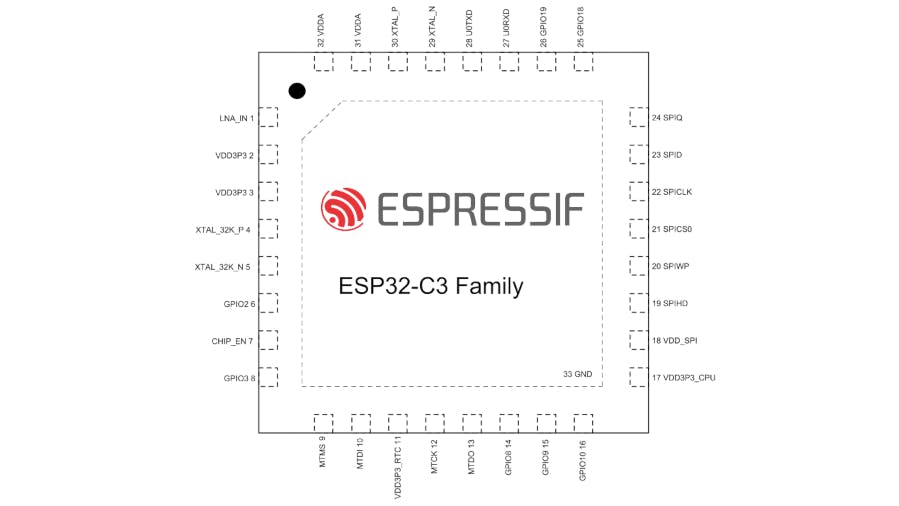

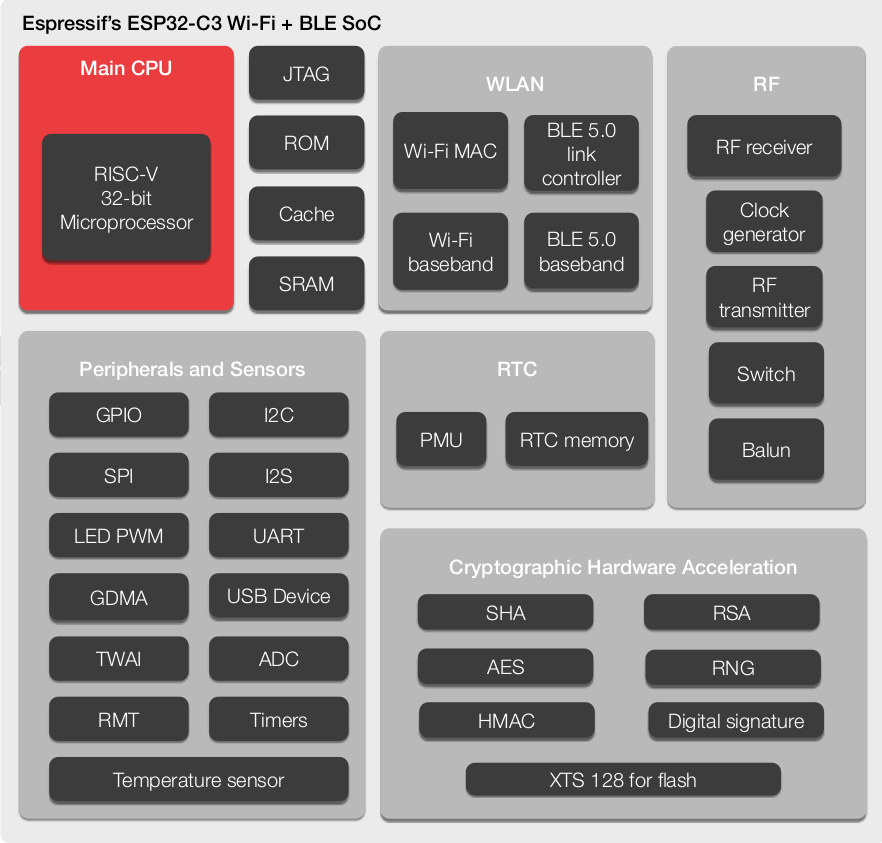

Espressif's ESP32-C3 Leaks as a Drop-In Pin-Compatible RISC-V Replacement for the Popular ESP8266 | Gareth Halfacree, hackster.io

Espressif's ESP32-C3 Leaks as a Drop-In Pin-Compatible RISC-V Replacement for the Popular ESP8266 | Gareth Halfacree, hackster.ioAfter the introduction of an ultra-low-power RISC-V core in the ESP32-S2, Espressif is looking to launch its first RISC-V-only part. Read the full article. ]]>

Description: The entire processor industry is currently going through a paradigm shift - new generations of domain-specific proprietary processor cores based on the open-source RISC-V ISA…

Description: The RISC-V ISA has opened tremendous opportunities creating a breeze of fresh air in the ARM dominated design houses of embedded SoC projects. We didn’t…

An Automated Scalable RISC-V Cache Coherency Verification Project | Breker Verification Systems

An Automated Scalable RISC-V Cache Coherency Verification Project | Breker Verification SystemsFind out more about Breker's RISC-V TrekApp: https://brekersystems.com/products/ri... Find out more about Breker's Cache Coherency TrekApp: https://brekersystems.com/products/ca...]]>

ESP32-C3 WiFi & BLE RISC-V processor is pin-to-pin compatible with ESP8266 | JEAN-LUC AUFRANC (CNXSOFT)

ESP32-C3 WiFi & BLE RISC-V processor is pin-to-pin compatible with ESP8266 | JEAN-LUC AUFRANC (CNXSOFT)ESP32-S2-MINI modules last September, we also noted Espressif teased us with ESP32-S3 and ESP32-C3 with close to no details. ESP32-S3 is expected to be a…

Building coreboot for RISC-V and running it in Qemu | Wojciech Niewiadomski, 3MDEB

Building coreboot for RISC-V and running it in Qemu | Wojciech Niewiadomski, 3MDEBRead the full article.]]>