RISC-V Raspberry Pi Alternative Edges Closer to Release | Ian Evenden, Toms Hardware

RISC-V Raspberry Pi Alternative Edges Closer to Release | Ian Evenden, Toms HardwareD1 puts RISC-V into the hands of makers everywhere A potential new Raspberry Pi competitor will soon be announced, according to a post on embedded…

Espressif’s ESP32-C6 brings the next generation wireless connectivity | Open Cloudware

Espressif’s ESP32-C6 brings the next generation wireless connectivity | Open CloudwareEspressif recently launched the ESP32-C6, which adds up to its long list of ESP32 series of SoCs. The ESP32-C6 is claimed to be the company’s…

SiFive Tapes Out Their First 5nm RISC-V Processor Core | Michael Larabel

SiFive Tapes Out Their First 5nm RISC-V Processor Core | Michael LarabelSiFive's OpenFive business unit announced today they have completed their first tape out of a RISC-V processor core using TSMC's 5nm process. This 5nm RISC-V…

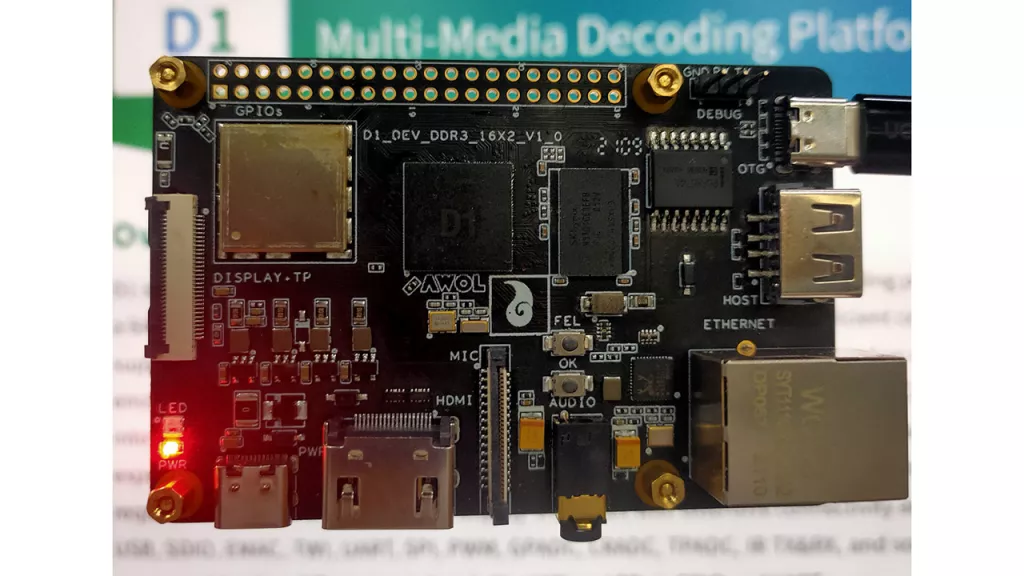

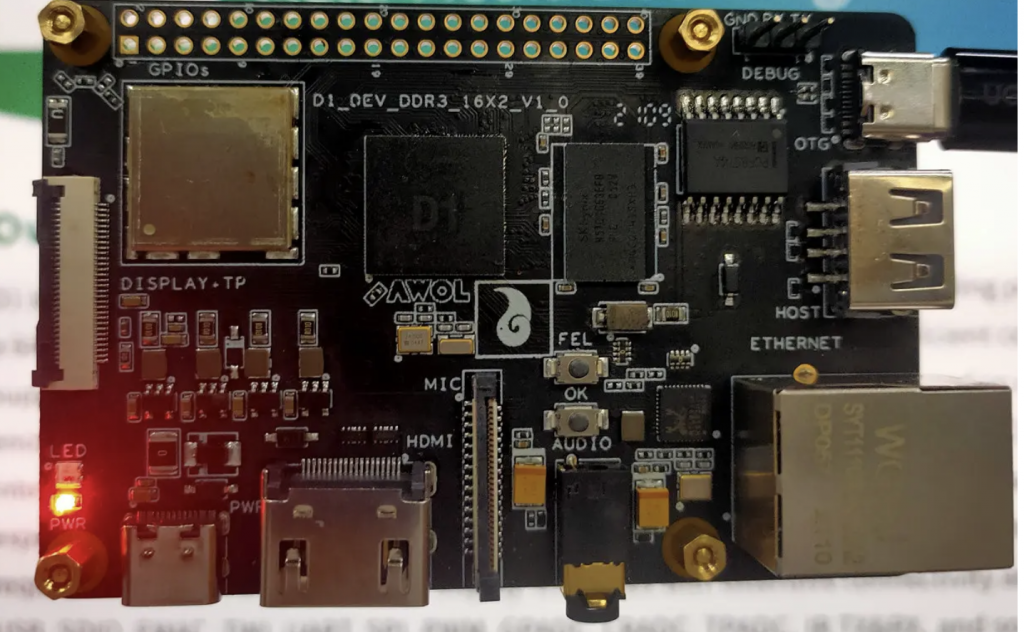

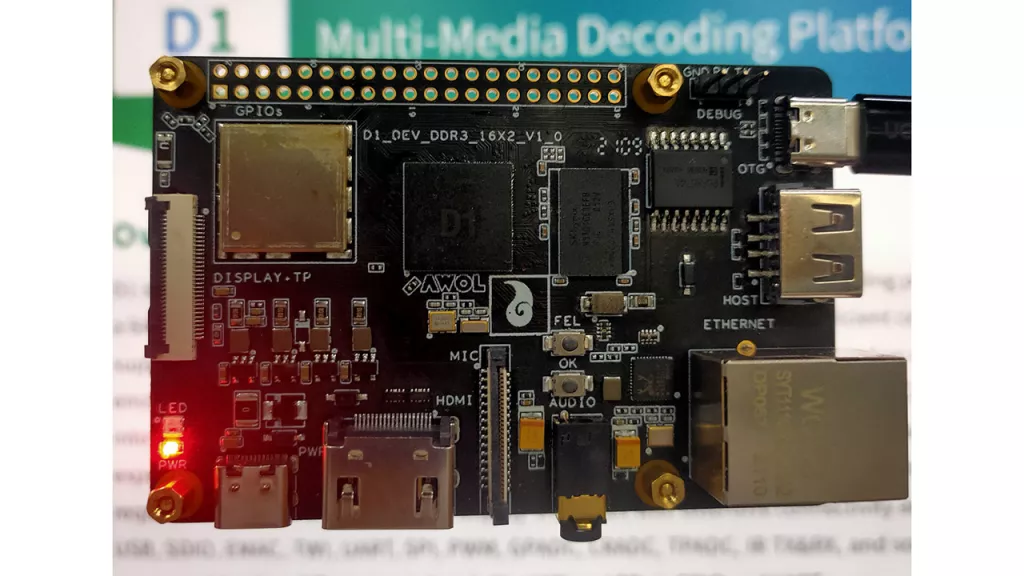

A first look at Allwinner D1 Linux RISC-V SBC and Processor | Jean-Luc Aufranc, CNX Soft

A first look at Allwinner D1 Linux RISC-V SBC and Processor | Jean-Luc Aufranc, CNX SoftLast year, we reported that Allwinner was working on an Alibaba XuanTie C906 based RISC-V processor that would be found in low-cost Linux capable single…

Homebrew RISC-V Computer Has Beauty and Brains | Tom Nardi, Hackaday

Homebrew RISC-V Computer Has Beauty and Brains | Tom Nardi, HackadayBuilding your own CPU is arguably the best way to truly wrap your head around how all those ones and zeros get flung around inside…

Low-Cost Single-Board Computers with RISC-V Chips are Coming Soon | Brad Linder, liliputing

Low-Cost Single-Board Computers with RISC-V Chips are Coming Soon | Brad Linder, liliputingThe first single-board computers powered by an Allwinner Xuantie-C906 processor could be set to ship soon. The chip isn’t exactly a speed demon, but it…

Video: The Future of RISC-V in HPC – Vadim Malenboim, Sr Field Application Engineer, SiFive Core IP

Video: The Future of RISC-V in HPC – Vadim Malenboim, Sr Field Application Engineer, SiFive Core IPRISC-V Architecture is widely adopted in the embedded and IoT market. The next phase of RISC-V Architecture evolution is the HPC segment. The SiFive portfolio…

SiFive Tapes Out First 5nm TSMC RISC-V Chip With 7.2 Gbps HBM3 | Anton Shilov, Tom’s Hardware

SiFive Tapes Out First 5nm TSMC RISC-V Chip With 7.2 Gbps HBM3 | Anton Shilov, Tom’s HardwareSiFive and OpenFive hit 5nm milestone. SiFive on Tuesday said that that its OpenFive division has successfully taped out the company's first system-on-chip (SoC) on TSMC's N5…

PQShield announces appointment of Ben Marshall, editor and main author of the RISC-V “K’ Cryptography Extension, to bolster its hardware division PQShield, the cybersecurity company…

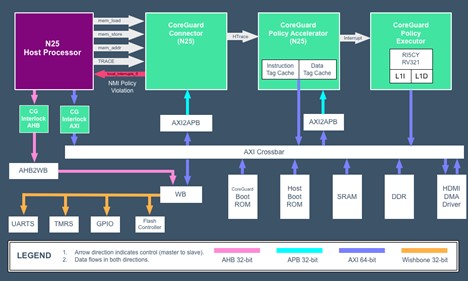

Building security into an AI SoC using CPU features with extensions | Marco Ciaffi, John Min, Embedded

Building security into an AI SoC using CPU features with extensions | Marco Ciaffi, John Min, EmbeddedWith the rapid deployment of artificial intelligence (AI), the focus of AI system on chip (SoC) design has been on building smarter, faster and cheaper…

ESP32-C6 WiFI 6 and Bluetooth 5 LE RISC-V SoC for IoT devices coming soon | JEAN-LUC AUFRANC (CNXSOFT)

ESP32-C6 WiFI 6 and Bluetooth 5 LE RISC-V SoC for IoT devices coming soon | JEAN-LUC AUFRANC (CNXSOFT)Espressif Systems introduced their first RISC-V wireless SoC last year with ESP32-C3 single-core 32-bit RISC-V SoC offering both 2.4GHz WiFi 4 and Bluetooth 5.0 LE…

New Part Day: Espressif Esp32-C6 Includes Wifi 6 and a RISC-V Core | Kerry Scharfglass, Hackaday

New Part Day: Espressif Esp32-C6 Includes Wifi 6 and a RISC-V Core | Kerry Scharfglass, HackadayIf you’re a reader of Hackaday, then you’ve almost certainly encountered an Espressif part. The twin microcontroller families ESP8266 and ESP32 burst onto the scene…

Read the full article (Spanish).]]>

Arm and RISC-V Software Development Solution from Ashling: RiscFree™ for Arm & RISC-V | Ashling (Press Release)

Arm and RISC-V Software Development Solution from Ashling: RiscFree™ for Arm & RISC-V | Ashling (Press Release)Read the full press release.]]>