The recent development of the RISC-V IOMMU effort has attracted substantial attention from the RISC-V community. Xuantie IOMMU from T-Head Semiconductors of Alibaba Group, holding…

The Mi-V RISC-V ecosystem is a continuously expanding, comprehensive suite of tools and design resources developed by Microchip and numerous third parties to fully support…

Introduction Among many new things in the 21st century, internet and IoT have been one of the most significant human advancements. As fast-paced and accelerating…

RISC-V RV32I JALR Instruction | Maven Silicon

RISC-V RV32I JALR Instruction | Maven SiliconThis video explains the RV32I JALR instruction. RISC-V is growing rapidly, follow this RISC-V video blog series to obtain knowledge about RISC-V processors, Instruction formats,…

FOSSi Explosion 2021 | Olof Kindgren, FOSSi Foundation and Qamcom

FOSSi Explosion 2021 | Olof Kindgren, FOSSi Foundation and QamcomDo you know what just happened? 2021 just happened. Most years has its ups and downs, but when it comes to 2021 it seems like…

Intel Corporation Makes Deep Investment in RISC-V Community to Accelerate Innovation in Open Computing

Intel Corporation Makes Deep Investment in RISC-V Community to Accelerate Innovation in Open ComputingRISC-V welcomes Intel to the Board of Directors to collaborate on RISC-V IP and contribute engineering expertise to accelerate RISC-V software development ZURICH – February…

RISC-V RV32I J-Type | Maven Silicon

RISC-V RV32I J-Type | Maven SiliconThis video explains the RV32I J-Type instructions. RISC-V is growing rapidly, follow this RISC-V video blog series to obtain knowledge about RISC-V processors, Instruction formats,…

Semico Research’s New Report Predicts There Will Be 25 Billion RISC-V-Based AI SoCs By 2027 | Rich Wawrzyniak, Semico Research Corporation

Semico Research’s New Report Predicts There Will Be 25 Billion RISC-V-Based AI SoCs By 2027 | Rich Wawrzyniak, Semico Research CorporationResearch underscores current RISC-V architecture momentum, emphasizing impressive growth in consumer, enterprise and communication markets RISC-V is leading the open era of computing across…

Our work together with Google and the world’s research community on detecting and mitigating the Rowhammer problem in DRAM memories has been proving that the…

Alibaba Cloud, the digital technology and intelligence backbone of Alibaba Group, announced it has opened the source code of Yun on Chip (YoC), its proprietary…

RISC-V RV32I S-Type | Maven Silicon

RISC-V RV32I S-Type | Maven SiliconThis video explains the RV32I S-Type instructions. RISC-V is growing rapidly, follow this RISC-V video blog series to obtain knowledge about RISC-V processors, Instruction formats,…

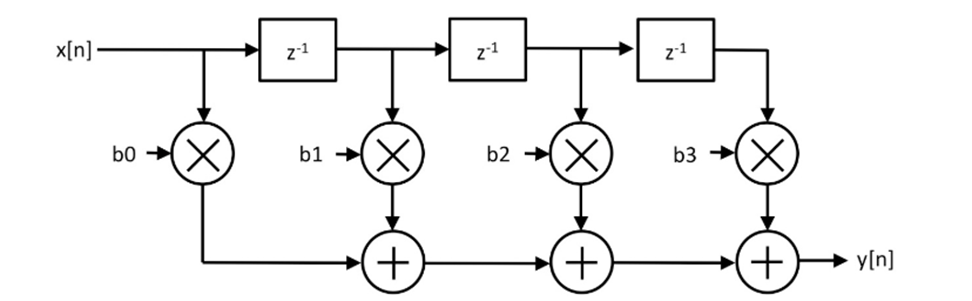

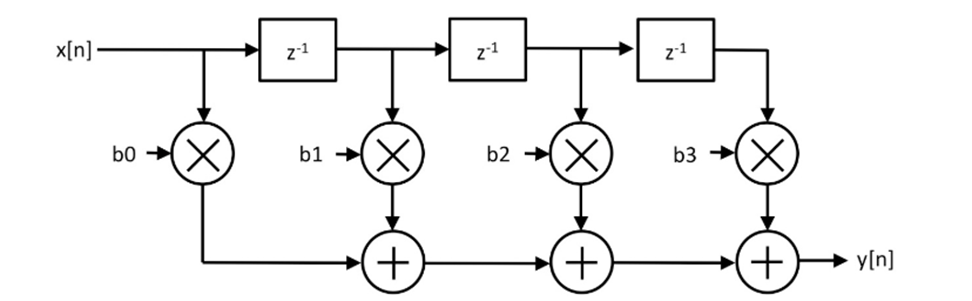

The integration of AI algorithms on end devices (“Edge AI”, “AI of Things”, TinyML,..) is conquering the domain of resource constrained microcontrollers and cost-efficient ASIC…

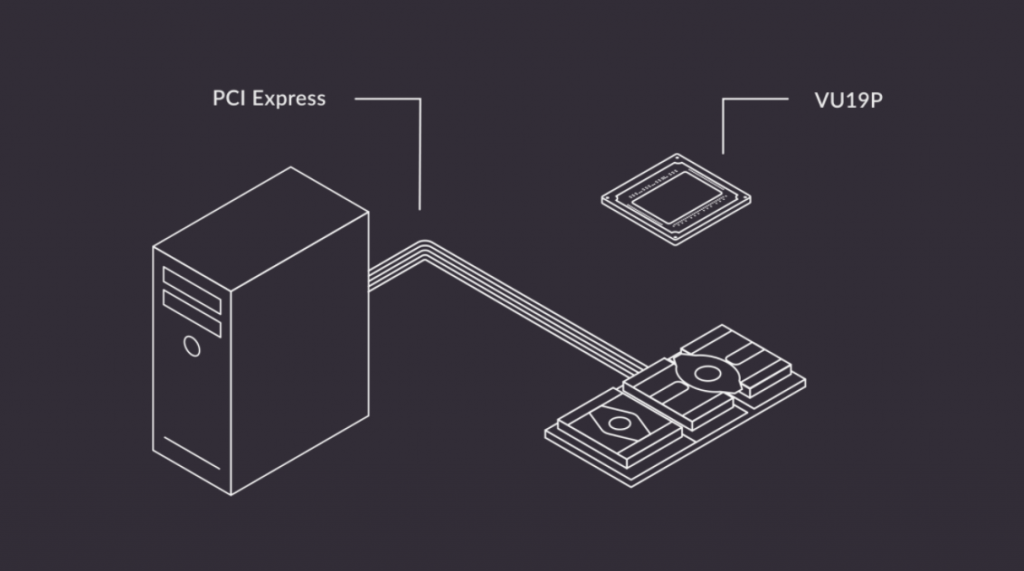

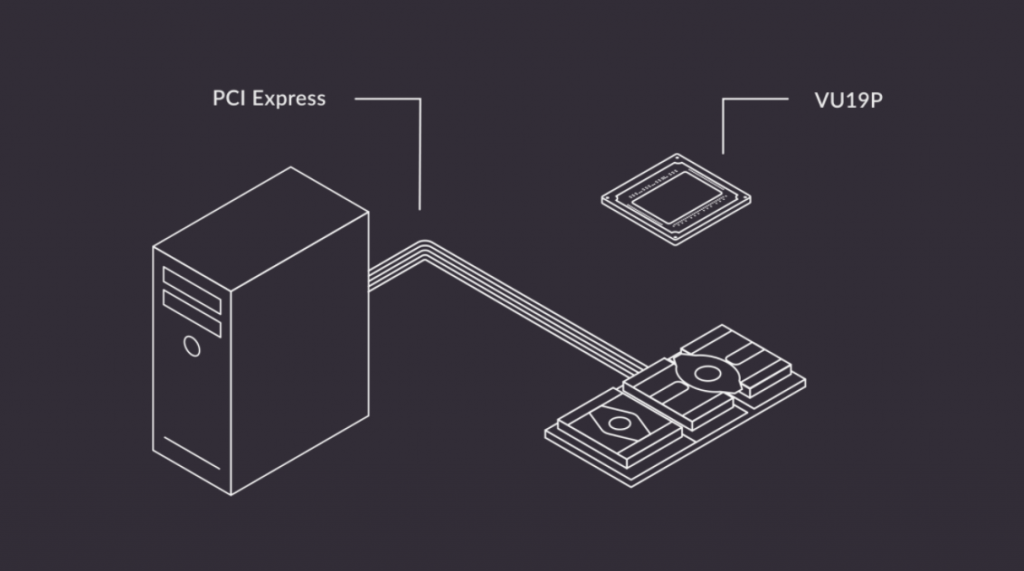

High-throughput open source PCIe on Xilinx VU19P-based ASIC prototyping platform

High-throughput open source PCIe on Xilinx VU19P-based ASIC prototyping platformOriginally published by Antmicro In the daily work at Antmicro, they use FPGAs primarily for their flexibility and parallel data processing capabilities that make…

Hardware Description Language Chisel & Diplomacy Deeper dive

Hardware Description Language Chisel & Diplomacy Deeper diveAre you using Chisel? A hardware building language based on Scala. Not a high-level synthesis language. SiFive's RISC-V IP use Chisel Rocket-Chip : https://github.com/chipsalliance/rocket-chip BOOM : https://github.com/riscv-boom/riscv-boom…

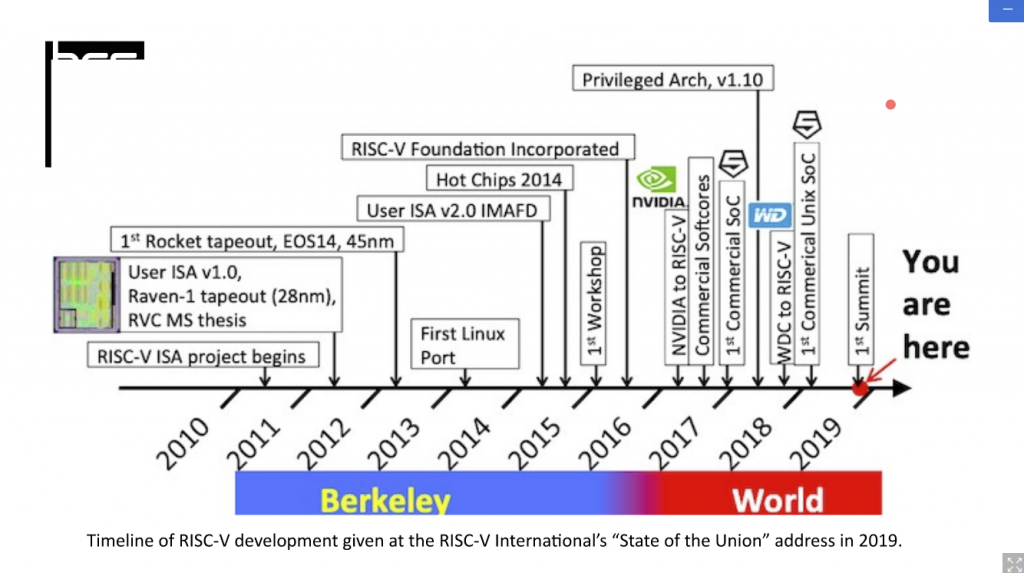

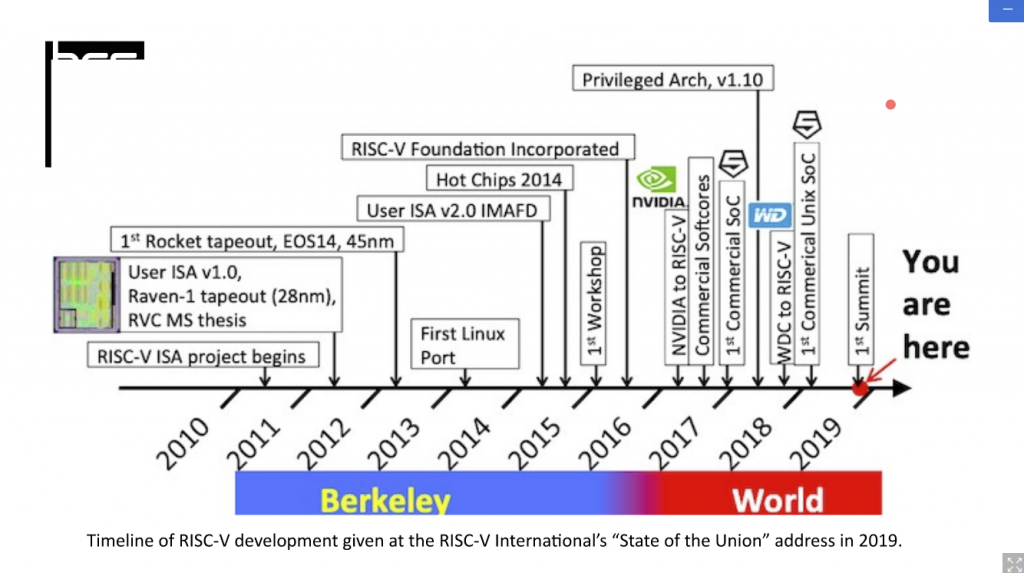

Where to start with RISC-V

Where to start with RISC-VOriginally posted on Medium How to get started, where to contribute, and what to do next RISC-V made the news recently when BeagleBoard.org revealed the…

Overview of Diplomacy for writing effective hardware design language Chisel (Japanese)

Overview of Diplomacy for writing effective hardware design language Chisel (Japanese)ハードウェア記述言語Chiselをもっともっと活用するためのDiplomacy概説 発表者:msyksphinz (FPGA開発日記著者) @msyksphinz_dev https://msyksphinz.hatenablog.com Chisel使ってますか? Scalaをベースとしたハードウェア構築言語. 高位合成言語ではない SiFiveのRISC-V IPで採用されている Rocket-Chip : https://github.com/chipsalliance/rocket-chip BOOM : https://github.com/riscv-boom/riscv-boom Chiselの基礎 : 「Chiselを始めたい人に読んで欲しい本」 https://nextpublishing.jp/book/12162.html ChiselがVerilogを生成するまで ChiselはScalaのDSLなので、Chisel CompilerはScalaで記述してある Chisel CompilerはFIR (Flexible Interpretation Representation)と呼ばれる中間言語を生成する…

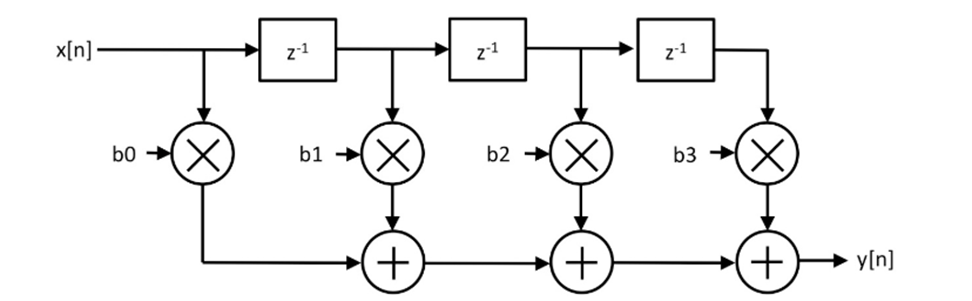

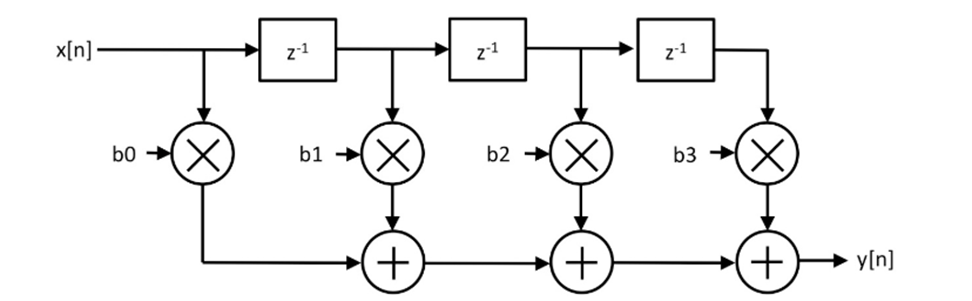

RISC-V CPU Performance | Maven Silicon

RISC-V CPU Performance | Maven SiliconThis video explains how Maven Silicon measures the CPU performance and how we try to improve the processor performance by improving its clock frequency and…

Let’s Make RISC-V Connected Systems Synonymous with Security

Let’s Make RISC-V Connected Systems Synonymous with SecurityThis blog was submitted by Silex Insight. If you are designing systems based on a RISC-V architecture, for example to run highly connected applications,…

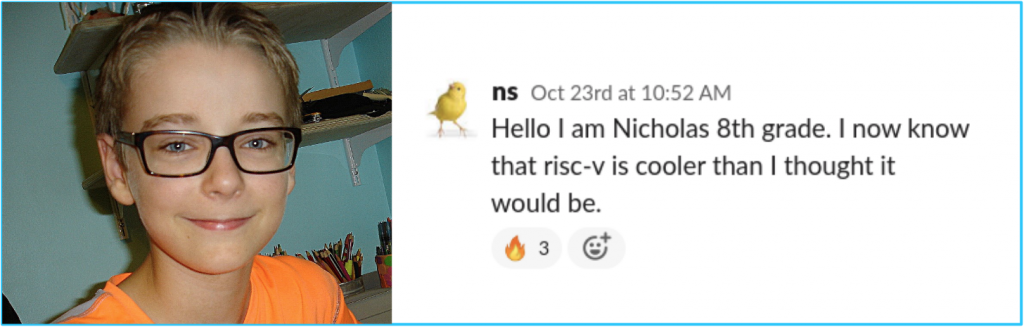

RISC-V Microarchitecture for Kids??!! | Steve Hoover, Redwood EDA

RISC-V Microarchitecture for Kids??!! | Steve Hoover, Redwood EDALast month I had the great pleasure of sharing a blog post about Nicholas Sharkey, an amazing 13 year-old who participated with graduate students and…

What is Processor Core Complexity?

What is Processor Core Complexity?This blog was originally published on the Codasip blog. The more complex a processor core, the larger the area and power consumption. But increasing…

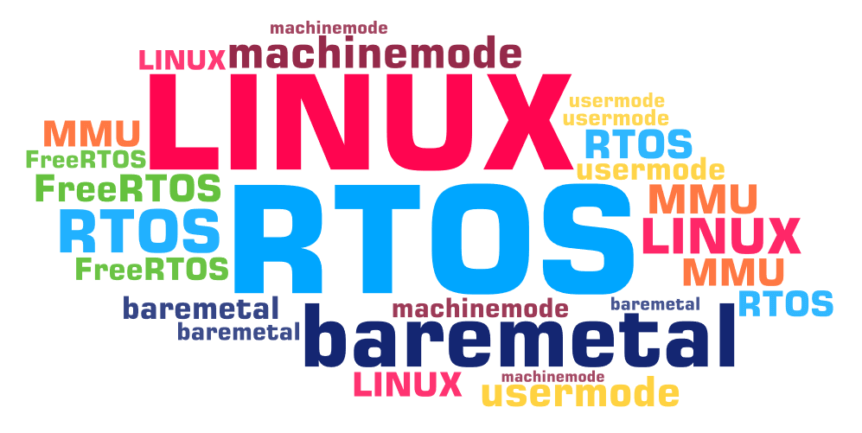

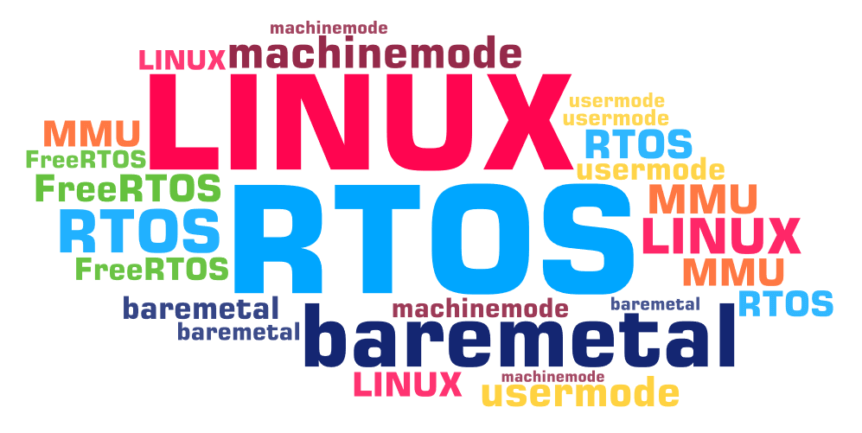

What is Needed to Support an Operating System?

What is Needed to Support an Operating System?This blog was originally published on the Codasip blog. For each embedded product, software developers need to consider whether they need an operating system;…

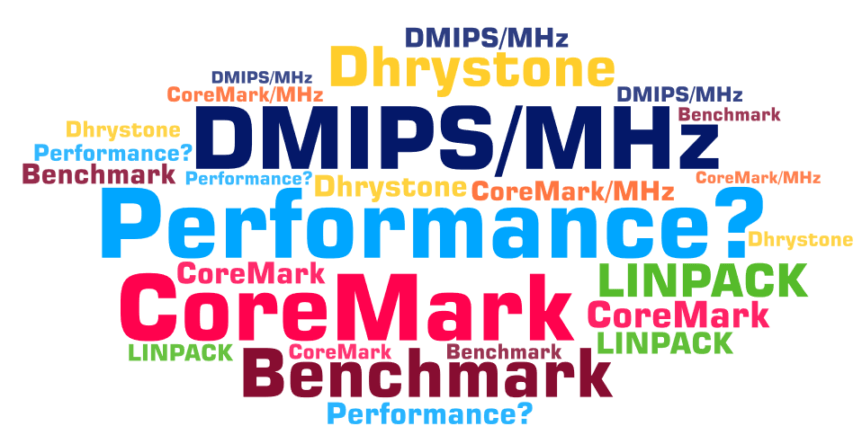

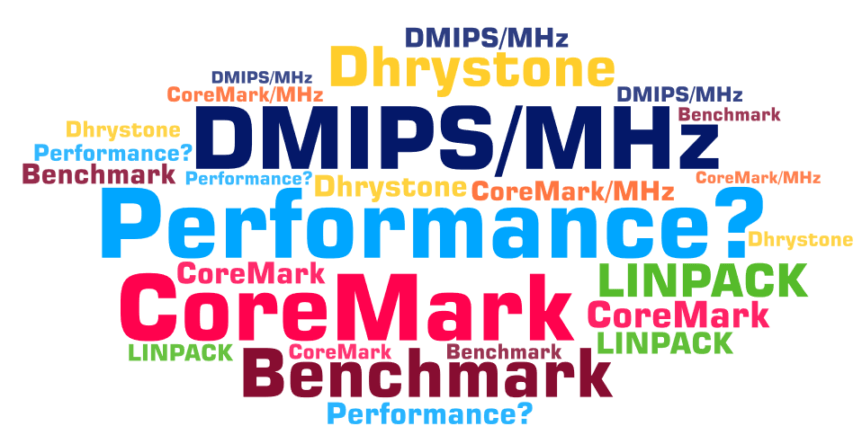

Understanding the Performance of Processor IP Cores

Understanding the Performance of Processor IP CoresThis blog was originally published on the Codasip blog. Looking at any processor IP, you will find that their vendors emphasise PPA (performance, power…

RPC DRAM support in open source DRAM controller

RPC DRAM support in open source DRAM controllerOriginal content published October 28, 2020 on the Antmicro blog. The Internet of Things is one of the areas that is hugely benefiting from miniaturization…

13-Year-Old, Nicholas Sharkey, Creates a RISC-V Core

13-Year-Old, Nicholas Sharkey, Creates a RISC-V CoreOne of my great pleasures operating my EDA startup, Redwood EDA, is working with enthusiastic college students and open-source developers and seeing how our technology…

High-throughput open source PCIe on Xilinx VU19P-based ASIC prototyping platform

High-throughput open source PCIe on Xilinx VU19P-based ASIC prototyping platformOriginally published by Antmicro In the daily work at Antmicro, they use FPGAs primarily for their flexibility and parallel data processing capabilities that make…

Hardware Description Language Chisel & Diplomacy Deeper dive

Hardware Description Language Chisel & Diplomacy Deeper diveAre you using Chisel? A hardware building language based on Scala. Not a high-level synthesis language. SiFive's RISC-V IP use Chisel Rocket-Chip : https://github.com/chipsalliance/rocket-chip BOOM : https://github.com/riscv-boom/riscv-boom…

Where to start with RISC-V

Where to start with RISC-VOriginally posted on Medium How to get started, where to contribute, and what to do next RISC-V made the news recently when BeagleBoard.org revealed the…

Overview of Diplomacy for writing effective hardware design language Chisel (Japanese)

Overview of Diplomacy for writing effective hardware design language Chisel (Japanese)ハードウェア記述言語Chiselをもっともっと活用するためのDiplomacy概説 発表者:msyksphinz (FPGA開発日記著者) @msyksphinz_dev https://msyksphinz.hatenablog.com Chisel使ってますか? Scalaをベースとしたハードウェア構築言語. 高位合成言語ではない SiFiveのRISC-V IPで採用されている Rocket-Chip : https://github.com/chipsalliance/rocket-chip BOOM : https://github.com/riscv-boom/riscv-boom Chiselの基礎 : 「Chiselを始めたい人に読んで欲しい本」 https://nextpublishing.jp/book/12162.html ChiselがVerilogを生成するまで ChiselはScalaのDSLなので、Chisel CompilerはScalaで記述してある Chisel CompilerはFIR (Flexible Interpretation Representation)と呼ばれる中間言語を生成する…

RISC-V CPU Performance | Maven Silicon

RISC-V CPU Performance | Maven SiliconThis video explains how Maven Silicon measures the CPU performance and how we try to improve the processor performance by improving its clock frequency and…

Let’s Make RISC-V Connected Systems Synonymous with Security

Let’s Make RISC-V Connected Systems Synonymous with SecurityThis blog was submitted by Silex Insight. If you are designing systems based on a RISC-V architecture, for example to run highly connected applications,…

RISC-V Microarchitecture for Kids??!! | Steve Hoover, Redwood EDA

RISC-V Microarchitecture for Kids??!! | Steve Hoover, Redwood EDALast month I had the great pleasure of sharing a blog post about Nicholas Sharkey, an amazing 13 year-old who participated with graduate students and…

What is Processor Core Complexity?

What is Processor Core Complexity?This blog was originally published on the Codasip blog. The more complex a processor core, the larger the area and power consumption. But increasing…

What is Needed to Support an Operating System?

What is Needed to Support an Operating System?This blog was originally published on the Codasip blog. For each embedded product, software developers need to consider whether they need an operating system;…

Understanding the Performance of Processor IP Cores

Understanding the Performance of Processor IP CoresThis blog was originally published on the Codasip blog. Looking at any processor IP, you will find that their vendors emphasise PPA (performance, power…

RPC DRAM support in open source DRAM controller

RPC DRAM support in open source DRAM controllerOriginal content published October 28, 2020 on the Antmicro blog. The Internet of Things is one of the areas that is hugely benefiting from miniaturization…

13-Year-Old, Nicholas Sharkey, Creates a RISC-V Core

13-Year-Old, Nicholas Sharkey, Creates a RISC-V CoreOne of my great pleasures operating my EDA startup, Redwood EDA, is working with enthusiastic college students and open-source developers and seeing how our technology…