Imperas Software Ltd., the leader in verification solutions for RISC-V, and Codasip, the leader in customizable RISC-V processor IP, today announced that Codasip has adopted…

Branch Target Cache [BTC] (part 3) Managing a speculative subroutine call stack

Branch Target Cache [BTC] (part 3) Managing a speculative subroutine call stackThis is the third of an occasional series of articles on the VRoom!/RVoom RISC-V CPU. This week a shorter update, we’re going to talk about…

RISC-V has been a very popular choice for embedded processor designs. Western Digital’s existing SweRV Core family is among the highest performance, area optimized embedded…

Open Hardware: Skyrocketing Momentum & Global Adoption from Embedded to Enterprise | Calista Redmond, RISC-V International

Open Hardware: Skyrocketing Momentum & Global Adoption from Embedded to Enterprise | Calista Redmond, RISC-V InternationalSee RISC-V International CEO Calista Redmond's keynote at Open Source Summit 2021 on Open Hardware: Skyrocketing Momentum and Global Adoption from Embedded to Enterprise. Watch…

FADU Technology Announces Speedy 14 GBps PCIe 5.0 SSD, up to 3.5 Million IOPS | Aaron Klotz, Tom’s Hardware

FADU Technology Announces Speedy 14 GBps PCIe 5.0 SSD, up to 3.5 Million IOPS | Aaron Klotz, Tom’s HardwareNew SSD offers nearly twice the bandwidth of Gen 4 NVMe drives. Just as mainstream computers begin adopting PCIe Gen 5 support, FADU Technology has…

理研、創薬専用スパコン開発 「RISC-V」アーキテクチャ採用、10万原子の挙動再現 | [井上輝一,ITmedia

理研、創薬専用スパコン開発 「RISC-V」アーキテクチャ採用、10万原子の挙動再現 | [井上輝一,ITmedia理化学研究所は11月18日、水やタンパク質など分子の動きのシミュレーションに特化した専用計算機「MDGRAPE-4A」を開発したと発表した。1秒間に約1300兆回(1.3ペタフロップス)の計算が可能で、タンパク質と薬剤、水分子などを合わせた計10万個の原子の動きを、現実的な時間で解析できる。「創薬の可能性を広げるもの」と理研は期待を掛ける。 Read the full article.

La compañía coreana FADU habría desarrollado una controladora RISC-V para la interfaz PCIe 5.0. Habitualmente se utiliza la arquitectura ARM para las controladoras, pero esta…

GCC Patches Pending For RISC-V’s Scalar Cryptography Extension | Michael Larabel, Phoronix

GCC Patches Pending For RISC-V’s Scalar Cryptography Extension | Michael Larabel, PhoronixPatches were recently sent out that implement support for RISC-V's Scalar Cryptography Extension within the GNU Compiler Collection. The RISC-V Scalar Cryptography Extension work recently…

Video: ESP32-C3 Modular IoT board – OBJEX Link RISC-V | Salvatore Raccardi

Video: ESP32-C3 Modular IoT board – OBJEX Link RISC-V | Salvatore RaccardiOBJEX Link RISC-V edition. This version of OBJEX Link "v1.6-C3" is based on the new ESP32-C3 which has a 32-bit single-core RISC-V processor. This version…

OBJEX Link v1.6-C3 RISC-V | Salvatore Raccardi, Hackster.io

OBJEX Link v1.6-C3 RISC-V | Salvatore Raccardi, Hackster.ioThis version of OBJEX Link v1.6-C3 is based on the new ESP32-C3 which has a 32-bit single-core RISC-V processor - (Bluetooth 5.0 and WiFi 4).…

Video: Kneron 2021 semiconductor product launch | Kneron

Video: Kneron 2021 semiconductor product launch | KneronWelcome to Kneron's 2021 semiconductor(KL530) product launch––join us in our explorations on the edge of next generation AI possibilities. Featured talks include "Future Automotives: The…

Выпущена первая партия российского RISC-V микроконтроллера “МК32 АМУР” | Sergey Karasev, Server News

Выпущена первая партия российского RISC-V микроконтроллера “МК32 АМУР” | Sergey Karasev, Server NewsКомпания «Микрон» сообщила о выпуске экспериментальной партии первого полностью российского микроконтроллера на открытой архитектуре RISC-V. Изделие под названием «МК32 АМУР» поможет снизить зависимость от иностранной…

Segger and Codasip Announce Cooperation on RISC-V

Segger and Codasip Announce Cooperation on RISC-VMonheim am Rhein & Munich, Germany – June 22nd, 2021 – SEGGER and Codasip announce that SEGGER’s J-Link debug probes and its Embedded Studio IDE…

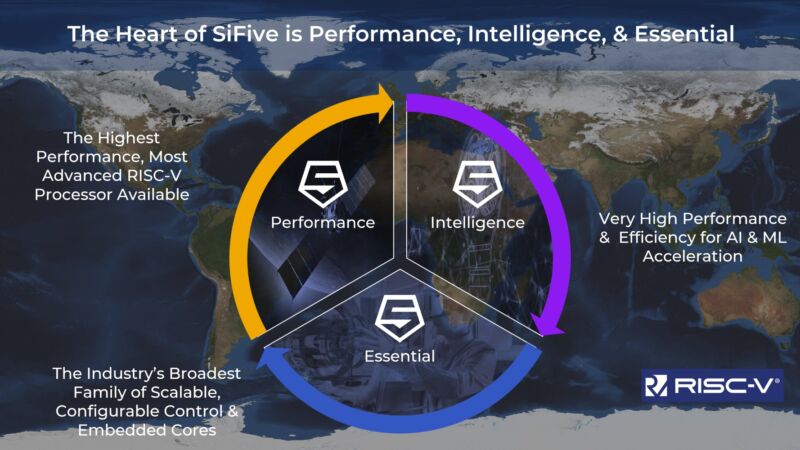

SiFive aims to challenge Arm with new tech, pairs with Intel on effort | Stephen Nellis, Reuters

SiFive aims to challenge Arm with new tech, pairs with Intel on effort | Stephen Nellis, ReutersJune 22 (Reuters) - SiFive Inc on Tuesday released a new computing chip design that aims to challenge Arm Ltd's dominance in smartphone chips and…

Life in a Formal Verification Lane | Shinavi Shah, SemiWiki.com

Life in a Formal Verification Lane | Shinavi Shah, SemiWiki.comThis summer, I got the opportunity to work as a Formal Verification Intern with Axiomise for six weeks. I’m a keen designer and love working…

x86 or x86-64 is the name of the architecture used by Intel and AMD to make their processors. RISC-V is a relatively new architecture that,…

SiFive’s brand-new P550 is one of the world’s fastest RISC-V CPUs | Jim Salter, arsTechnica

SiFive’s brand-new P550 is one of the world’s fastest RISC-V CPUs | Jim Salter, arsTechnicaToday's RISC-V microcontrollers may lead to future RISC-V phones and laptops. Today, RISC-V CPU design company SiFive launched a new processor family with two core…

LEMONT, Ill., OAK RIDGE, Tenn., and EDINBURGH, England, June 17, 2021 — Argonne National Laboratory (Argonne) in collaboration with Oak Ridge National Laboratory (ORNL), has…

SEGGER and Codasip Announce Cooperation on RISC-V

SEGGER and Codasip Announce Cooperation on RISC-VSEGGER and Codasip announce that SEGGER’s J-Link debug probes and its Embedded Studio IDE fully support Codasip’s RISC-V processors, right out-of-the-box. SEGGER’s J-Link debug probe…

Alibaba’s chip unit realizes key breakthroughs with Xuantie CPU | Global Times

Alibaba’s chip unit realizes key breakthroughs with Xuantie CPU | Global TimesThe semiconductor division of Chinese tech giant Alibaba Group announced on Tuesday that its self-developed Xuantie embedded central processing unit (CPU) has made technological breakthroughs…