Truechip Introduces Silicon IP for Network on Chip (NOC) Focused for TileLink RISC-V Chips | Truechip

Truechip Introduces Silicon IP for Network on Chip (NOC) Focused for TileLink RISC-V Chips | TruechipTruechip, the Verification IP Specialist, today announced that it has introduced a Silicon IP to its product offering in addition to its existing Verification IP…

Build an open source-hardware Allwinner D1s RISC-V Linux SBC for under $10 | Jean-Luc Aufranc, CNX Software

Build an open source-hardware Allwinner D1s RISC-V Linux SBC for under $10 | Jean-Luc Aufranc, CNX SoftwareWe covered Allwinner D1s RISC-V processor with 64MB built-in RAM a few days ago, and we’ve just found out about Xassette-Asterisk, an open-source hardware board…

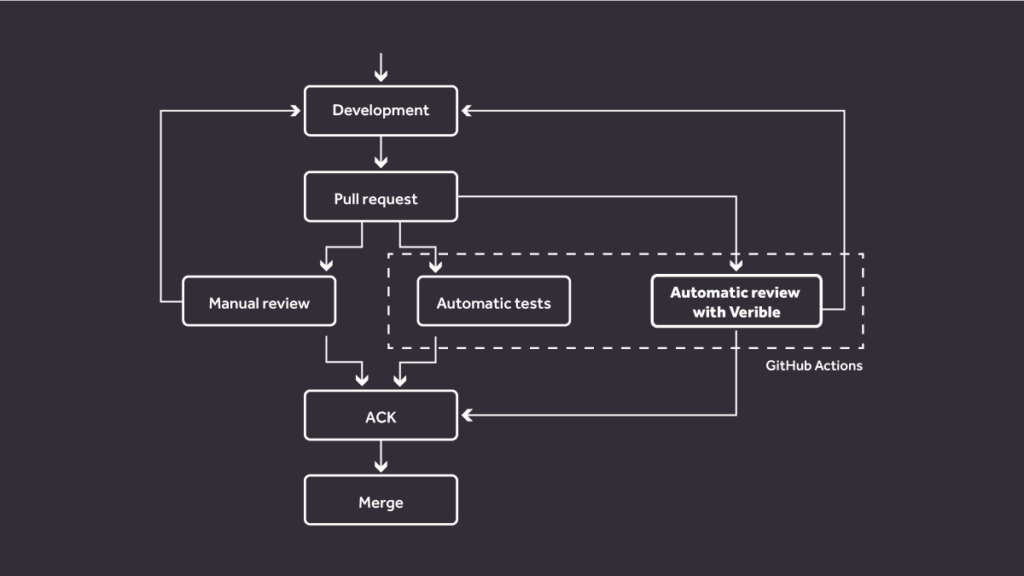

Automatic SystemVerilog linting in GitHub Actions with Verible | Antmicro

Automatic SystemVerilog linting in GitHub Actions with Verible | AntmicroWith the recent advances in open source ASIC development tools such as Verible, it has become easier to automate tasks and boost developer productivity. The Verible linter…

RISC-V RV32I I-Type | Maven Silicon

RISC-V RV32I I-Type | Maven SiliconThis video explains the RV32I I-Type instructions. RISC-V is growing rapidly, follow this RISC-V video blog series to obtain knowledge about RISC-V processors, Instruction formats,…

Tiny SBC runs Linux on new RAM-equipped Allwinner RISC-V SoC |

Tiny SBC runs Linux on new RAM-equipped Allwinner RISC-V SoC |MangoPi is prepping a tiny “MangoPi-MQ1” SBC with the new Allwinner F133-A (D1s), a spin-down of Allwinner’s D1 that adds 64MB RAM. Both SoCs use…

Supporting masking countermeasures for non-invasive side-channel security in instructions set architectures is a hard problem. Masked operations often have a large number of inputs and…

Sneak peek into SiFive’s most powerful RISC-V yet | Steve Bush, Electronics Weekly

Sneak peek into SiFive’s most powerful RISC-V yet | Steve Bush, Electronics WeeklySo far only called ‘Next Generation Core’ or Next-Gen, its official name, final design specs and availability will be unveiled early in December at the…

Video: 5 Stage Pipeline: RISC-V Processor In TS (part 3) | Low Level JavaScript

Video: 5 Stage Pipeline: RISC-V Processor In TS (part 3) | Low Level JavaScriptRISC-V CPU in TypeScript: Emulator Watch the full video.

Codasip boosts Studio processor design tools | Neil Tyler, New Electronics

Codasip boosts Studio processor design tools | Neil Tyler, New ElectronicsCodasip, a supplier of customisable RISC-V processor IP and tools, has announced further enhancements to its Studio processor design toolset. New features in Studio 9.1…

RISC-V-Based VEGA Brings Continual Learning to TinyML with an Order of Magnitude Efficiency Gain | Gareth Halfacree, Hackster.io

RISC-V-Based VEGA Brings Continual Learning to TinyML with an Order of Magnitude Efficiency Gain | Gareth Halfacree, Hackster.ioBased on the PULP Platform, this RISC-V chip could offer hundreds of thousands of hours of operation on a single battery charge. A team of…

MangoPi-MQ1 Is an Ultra-Compact, Soon-to-be-Open Source Allwinner D1 RISC-V Dev Board | Gareth Halfacree, Hackster.io

MangoPi-MQ1 Is an Ultra-Compact, Soon-to-be-Open Source Allwinner D1 RISC-V Dev Board | Gareth Halfacree, Hackster.ioSingle-board computer startup MangoPi has shown off prototypes of a low-cost development board based on the recently-open sourced XuanTie C906 RISC-V core — and promises…

New Allwinner RISC-V Chip Uncovered on Tiny Board | Ian Evenden, Tom’s Hardware

New Allwinner RISC-V Chip Uncovered on Tiny Board | Ian Evenden, Tom’s HardwareReduced instruction set, reduced size. A new version of the Allwinner D1 RISC-V media board has come to light (via CNX Software). The D1s, also…

Keynote Session: Hypervisor Extensions in RISC-V - Robert Eshleman, Vates SAS This talk presents the virtualization capabilities offered by the RISC-V Hypervisor ISA extension (H…

SEGGER’s emRun Runtime Library Licensed by SiFive for Superior Code Size and Performance Improvements | Design & Reuse

SEGGER’s emRun Runtime Library Licensed by SiFive for Superior Code Size and Performance Improvements | Design & ReuseMonheim am Rhein, Germany – May 31, 2021 -- The SEGGER emRun runtime library is available as part of the recently announced SiFive 21G1 release. SiFive’s…

Are we seeing the takeover from RISC-V? | Electropages, Robin Mitchell

Are we seeing the takeover from RISC-V? | Electropages, Robin MitchellThe RISC-V architecture, which is in direct competition with ARM, is making more news headlines recently. So how do RISC-V and ARM differ, what products…

Alibaba is making its cloud OS compatible with multiple chip architectures | TechCrunch, Rita Liao

Alibaba is making its cloud OS compatible with multiple chip architectures | TechCrunch, Rita LiaoAlibaba’s cloud computing unit is making its Apsara operating system compatible with processors based on Arm, x86, RISC-V, among other architectures, the company announced at a conference on…

This talk is on the technical paper presented at DVCon 2021. Abstract: The open RISC-V instruction set architecture is gaining traction with both semiconductor vendors…

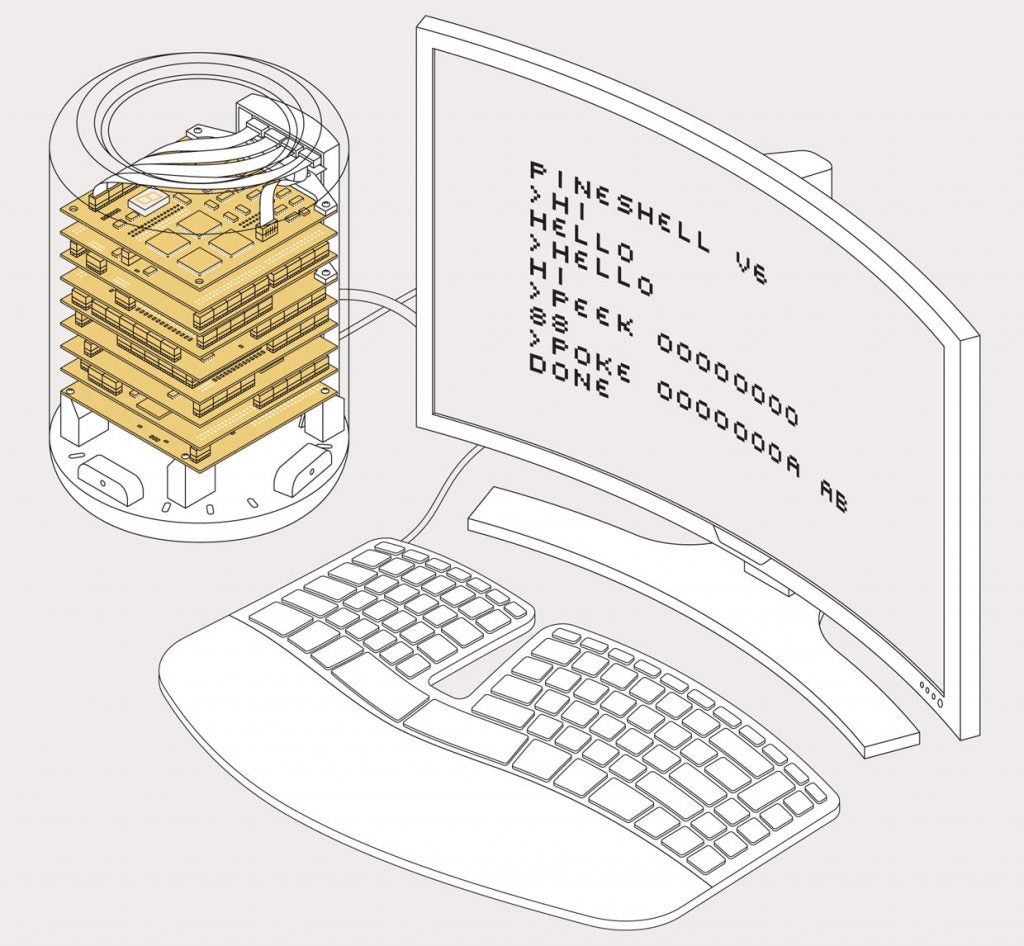

Build a RISC-V CPU From Scratch | Filip Szkandera

Build a RISC-V CPU From Scratch | Filip SzkanderaIt’s a certain kind of itch that drives people to voluntarily build their own CPU. We start thinking about the papered-over gap in our understanding, the…

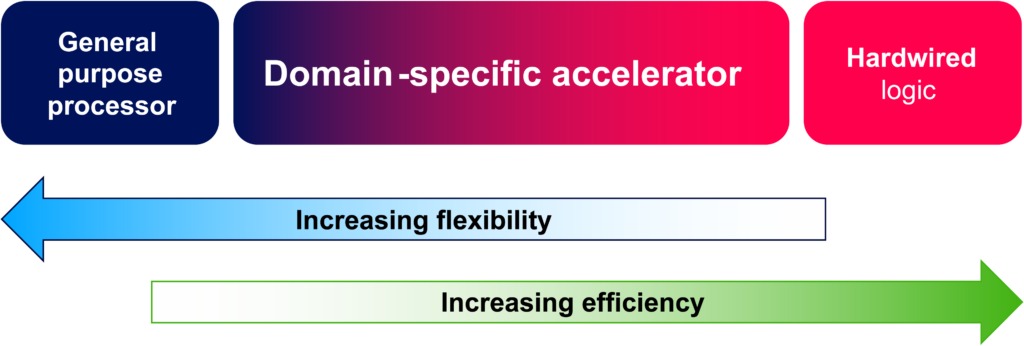

Domain-Specific Accelerators | Codasip

Domain-Specific Accelerators | CodasipSEMICONDUCTOR SCALING HAS FUNDAMENTALLY CHANGED For about fifty years, IC designers have been relying on different types of semiconductor scaling to achieve gains in performance.…

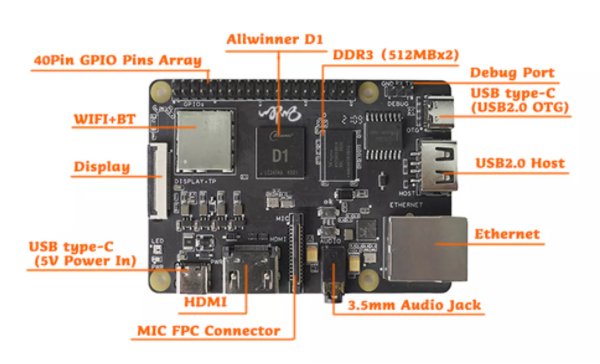

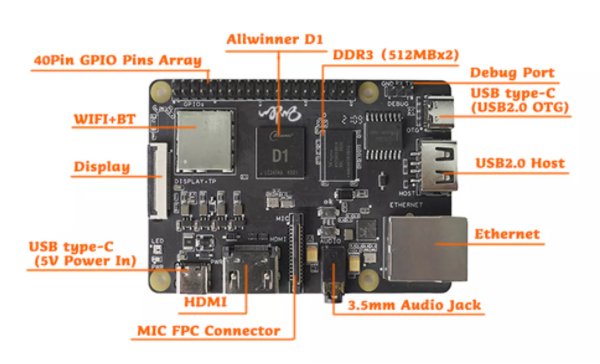

Nezha RISC-V Linux SBC launched for $99 and up | JEAN-LUC AUFRANC, CNX Software

Nezha RISC-V Linux SBC launched for $99 and up | JEAN-LUC AUFRANC, CNX SoftwareLast month, we wrote about Allwinner D1 SBC & processor that promised to offer a relatively low-cost RISC-V Linux solution. We were not given a name at…

HiFive Unmatched RISC-V computer board is now shipping | Brad Linder, liliputing

HiFive Unmatched RISC-V computer board is now shipping | Brad Linder, liliputingAt first glance, the HiFive Unmatched from SiFive looks like just another mini ITX computer motherboard. But rather than an x86 chip, this system is powered by…

Low Cost Raspberry Pi Alternative RISC-V Board Starts Crowdfunding | Ian Evenden, Tom’s Hardware

Low Cost Raspberry Pi Alternative RISC-V Board Starts Crowdfunding | Ian Evenden, Tom’s HardwareThe 64bit RISC-V Raspberry Pi alternative we wrote about last month has turned up again, this time on Indiegogo, with a new name. The Nezha board, named after a protective…

May 21, 2021 -- Your next MCU needs to be more than just smart. It needs to be power-efficient, have ample memory, and industrial-grade security.…