RISC-V Summit North America T-Shirt Design Contest—And the Winner Is…!

RISC-V Summit North America T-Shirt Design Contest—And the Winner Is…!In a nod to the creativity and innovation of the RISC-V community, this year RISC-V International hosted the first RISC-V Summit North America T-shirt design…

Authors: Tony Chen, Nathaniel Wesley Filardo, Kunyan Liu, Robert Norton-Wright, Yucong Tao CHERIoT (Capability Hardware Extension to RISC-V for Internet of Things) is a 32-bit…

Join the ranks of RISC-V Advocates!

Join the ranks of RISC-V Advocates!We are looking for RISC-V enthusiasts from around the world to become key players in supporting RISC-V progress through global promotion and engagement. As an…

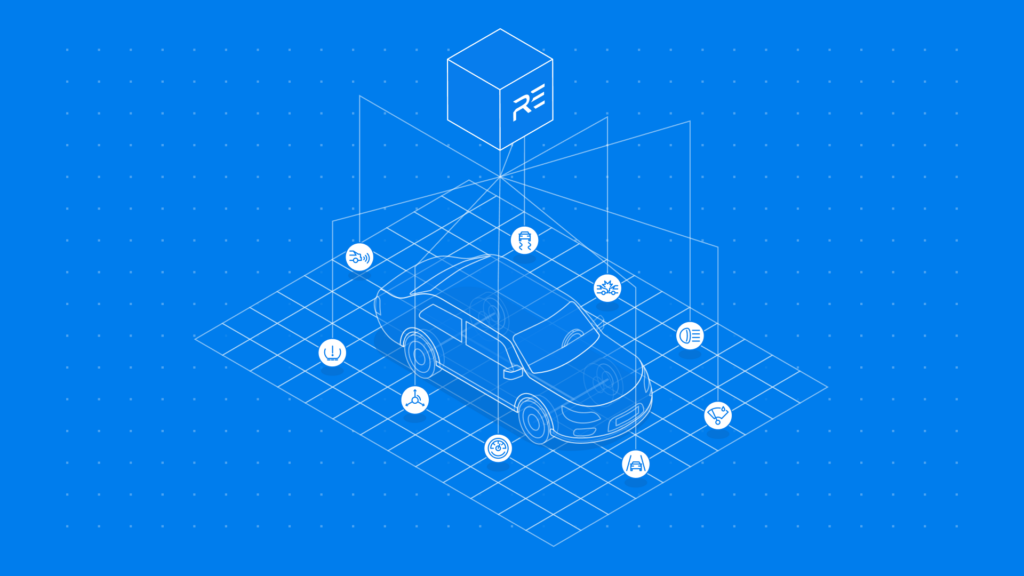

Infineon Harnesses the Power of RISC-V for Next-Generation Automotive MCU Innovation

Infineon Harnesses the Power of RISC-V for Next-Generation Automotive MCU InnovationBy: Thomas Böhm - SVP Automotive Microcontroller, Infineon One of the megatrends in the automotive industry is the Software Defined Vehicle (SDV), where major innovations…

Featured Work: Microarchitecture Security: The Spectre Affair

Featured Work: Microarchitecture Security: The Spectre AffairAuthor: Ronan Lashermes, Hardware Security Research Engineer at Inria. Results from a joint work with Hery Andrianatrehina, Joseph Paturel, Simon Rokicki and Thomas Rubiano at…

The DC-ROMA Laptop II has undergone comprehensive upgrades in both hardware and software, offering enhanced computing power and energy efficiency, as well as extensive system…

Exploring the RISC-V Summit 2024: Technical Sessions Announced

Exploring the RISC-V Summit 2024: Technical Sessions AnnouncedThe RISC-V Summit North America Plenary Sessions are now live on the event website. Each year, we are continually impressed with the high caliber of…

Trailblazers: Board of Directors Technical Award Winners 2024

Trailblazers: Board of Directors Technical Award Winners 2024By: Iris Zheng, Digital Marketing Intern, RISC-V International Five technical leaders were honored at RISC-V Summit Europe 2024 for their remarkable contributions to the RISC-V…

SpacemiT Key Stone K1 AI CPU has been adapted to the Fedora operating system successfully. With the Fedora operating system successfully running on the MUSE…

More than 1,300 Attendees Expected at RISC-V Summit China Next Week

More than 1,300 Attendees Expected at RISC-V Summit China Next WeekCheck out all the impressive talks and co-located events Next week, from August 21-23, more than 1,300 attendees will gather at the Huanglong Hotel in…

Microchip, and O.C.E. Technology deliver high-reliability RTOS for Polarfire® SoC FPGA space applications

Microchip, and O.C.E. Technology deliver high-reliability RTOS for Polarfire® SoC FPGA space applicationsBy: Barry Kavanagh, Chief Executive Officer, O.C.E. Technology Ltd. Polarfire® SoC FPGA RISC-V space applications can now take advantage of an RTOS compliant to ESA…

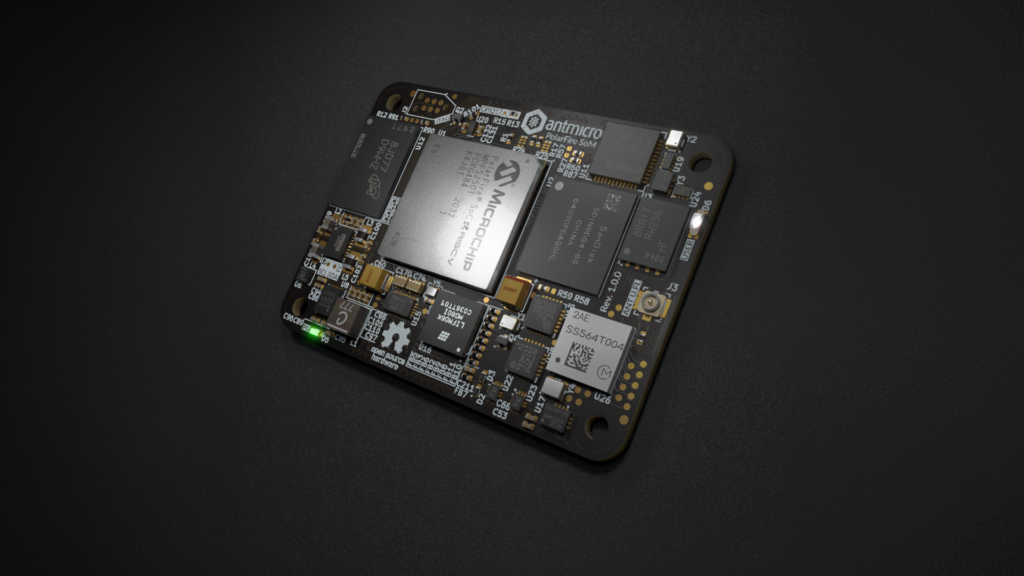

Open source System on Module with Microchip PolarFire SoC

Open source System on Module with Microchip PolarFire SoCThe PolarFire SoC was the world’s first Linux-enabled mass market multi-core RISC-V SoC, originally made available pre-silicon by Microchip through Antmicro’s Renode simulation framework. Thanks…

Redmond joins the RISC-V Foundation from IBM to continue to grow RISC-V membership, community engagement and market adoption The RISC-V Foundation, a non-profit corporation controlled by…

This statement was issued in 2018, and remains accurate today. Recent articles in the media have raised awareness around the processor security vulnerabilities named Meltdown and Spectre. These vulnerabilities are…

Porting and Optimizing Android ART on XuanTie C910

Porting and Optimizing Android ART on XuanTie C910By Lifang Xia Over the past three years, our team has undertaken the substantial task of porting Android 10 and Android 12 to the XuanTie…

Developing and testing heterogeneous space-grade systems with Renode

Developing and testing heterogeneous space-grade systems with RenodeWhile landing humans on the Moon was a feat accomplished with very basic compute power of 2MHz provided by the Apollo Guidance Computer, modern spacecraft…

Announcing The Fourth International Workshop on RISC-V for HPC

Announcing The Fourth International Workshop on RISC-V for HPCThe RISC-V HPC Special Interest Group is organising a workshop at ISC24, one of the leading High Performance Computing (HPC) conferences. The workshop will run…

Integrating ROS 2 With Microchip’s PolarFire® SoC FPGA

Integrating ROS 2 With Microchip’s PolarFire® SoC FPGAROS (Robot Operating System) is a popular open-source framework used for creating robotics applications. It provides a set of tools and libraries for building complex…

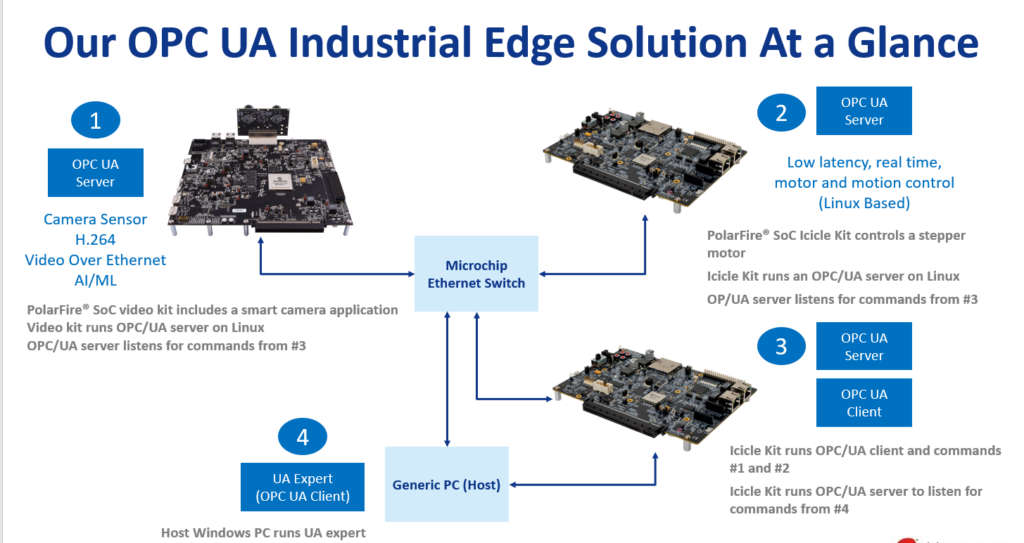

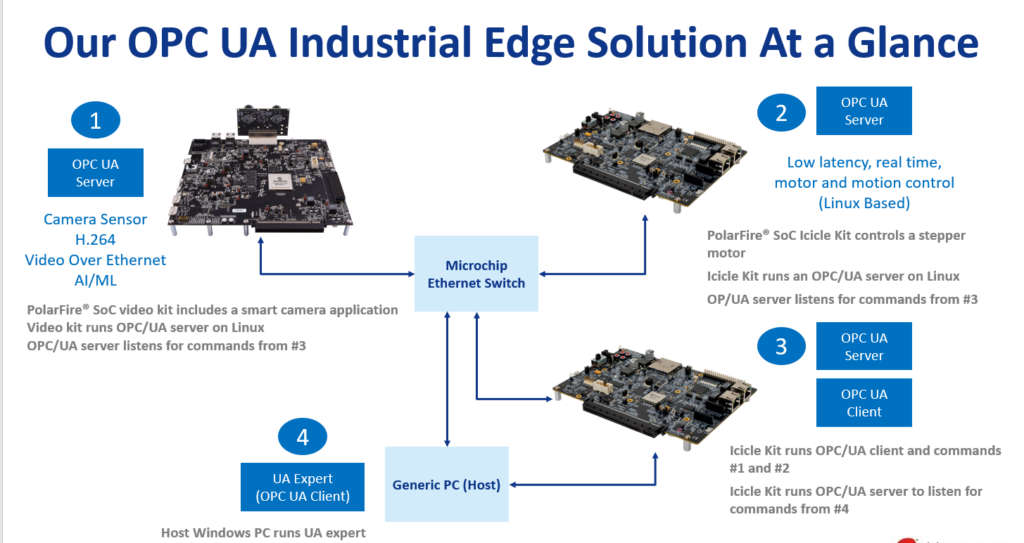

OPC UA on PolarFire SoC: Enabling Industrial Edge Solutions

OPC UA on PolarFire SoC: Enabling Industrial Edge SolutionsWebpage: https://www.microchip.com/en-us/solutions/industrial/fpga/opc-ua Author: Apurva Peri, Principal Engineer, FPGA Product Marketing The Modern Industrial Edge The Industrial Edge has become the standard for industrial automation requirements,…

Author- Rich Wawrzyniak Principal Analyst at The SHD Group As we start 2024, The SHD Group has released a comprehensive market analysis report titled "RISC-V…

Expanding RISC-V support in Renode with Bit-Manipulation extensions

Expanding RISC-V support in Renode with Bit-Manipulation extensionsAntmicro’s open source Renode simulation framework offers support for various instruction set architectures, with the RISC-V ISA being a major focus for – as a…

Five years of SERVing

Five years of SERVingAuthor: Olof Kindgren Making your own RISC-V CPU is a terrible idea. I have said that many times before. There are already a million RISC-V…

The Top 10 RISC-V Milestones & Highlights from 2023

The Top 10 RISC-V Milestones & Highlights from 2023Looking back at 2023, there are many different ways to measure progress and success. You could point to the growing adoption of RISC-V—which is in…

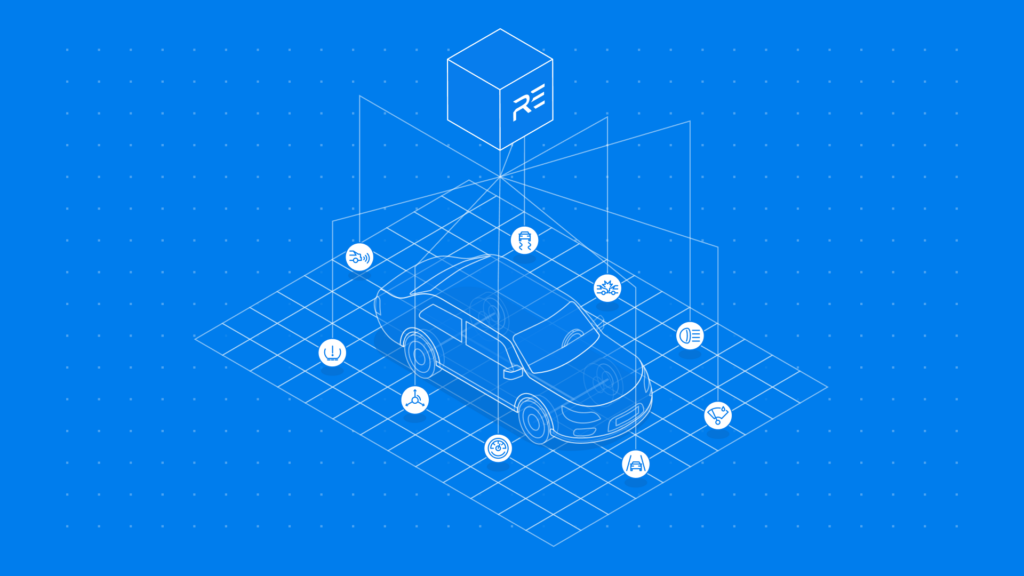

Developing and testing with Renode in heterogeneous, multi-node automotive use cases

Developing and testing with Renode in heterogeneous, multi-node automotive use casesAutomotive engineering in the past 30 years has been transformed by the growing capabilities of microprocessors, enabling their use in a wide range of the…

Solving bus and software deadlock problems in complex SoCs

Solving bus and software deadlock problems in complex SoCsBy: Siemens | Tessent Embedded Analytics | Author: Huw Geddes, Product Manager Intermittent bus and software deadlocks are amongst the toughest problems for development teams…

Porting and Optimizing Android ART on XuanTie C910

Porting and Optimizing Android ART on XuanTie C910By Lifang Xia Over the past three years, our team has undertaken the substantial task of porting Android 10 and Android 12 to the XuanTie…

Developing and testing heterogeneous space-grade systems with Renode

Developing and testing heterogeneous space-grade systems with RenodeWhile landing humans on the Moon was a feat accomplished with very basic compute power of 2MHz provided by the Apollo Guidance Computer, modern spacecraft…

Announcing The Fourth International Workshop on RISC-V for HPC

Announcing The Fourth International Workshop on RISC-V for HPCThe RISC-V HPC Special Interest Group is organising a workshop at ISC24, one of the leading High Performance Computing (HPC) conferences. The workshop will run…

Integrating ROS 2 With Microchip’s PolarFire® SoC FPGA

Integrating ROS 2 With Microchip’s PolarFire® SoC FPGAROS (Robot Operating System) is a popular open-source framework used for creating robotics applications. It provides a set of tools and libraries for building complex…

OPC UA on PolarFire SoC: Enabling Industrial Edge Solutions

OPC UA on PolarFire SoC: Enabling Industrial Edge SolutionsWebpage: https://www.microchip.com/en-us/solutions/industrial/fpga/opc-ua Author: Apurva Peri, Principal Engineer, FPGA Product Marketing The Modern Industrial Edge The Industrial Edge has become the standard for industrial automation requirements,…

Author- Rich Wawrzyniak Principal Analyst at The SHD Group As we start 2024, The SHD Group has released a comprehensive market analysis report titled "RISC-V…

Expanding RISC-V support in Renode with Bit-Manipulation extensions

Expanding RISC-V support in Renode with Bit-Manipulation extensionsAntmicro’s open source Renode simulation framework offers support for various instruction set architectures, with the RISC-V ISA being a major focus for – as a…

Five years of SERVing

Five years of SERVingAuthor: Olof Kindgren Making your own RISC-V CPU is a terrible idea. I have said that many times before. There are already a million RISC-V…

The Top 10 RISC-V Milestones & Highlights from 2023

The Top 10 RISC-V Milestones & Highlights from 2023Looking back at 2023, there are many different ways to measure progress and success. You could point to the growing adoption of RISC-V—which is in…

Developing and testing with Renode in heterogeneous, multi-node automotive use cases

Developing and testing with Renode in heterogeneous, multi-node automotive use casesAutomotive engineering in the past 30 years has been transformed by the growing capabilities of microprocessors, enabling their use in a wide range of the…

Solving bus and software deadlock problems in complex SoCs

Solving bus and software deadlock problems in complex SoCsBy: Siemens | Tessent Embedded Analytics | Author: Huw Geddes, Product Manager Intermittent bus and software deadlocks are amongst the toughest problems for development teams…