Bluespec, Inc. Releases Ultra-Low Footprint RISC-V Processor Family for Xilinx FPGAs, Offers Free Quick-Start Evaluation | Design & Reuse

Bluespec, Inc. Releases Ultra-Low Footprint RISC-V Processor Family for Xilinx FPGAs, Offers Free Quick-Start Evaluation | Design & ReuseBluespec, Inc., a founding member of RISC-V International and supplier of RISC-V Processor IP and tools, released the MCU RISC-V processor family targeted at ultra-low…

VS Code Venus RISC-V extension 1.0.0 released | Stefan Wallentowitz, RISC-V @ HM

VS Code Venus RISC-V extension 1.0.0 released | Stefan Wallentowitz, RISC-V @ HMWe have released the first public stable version of our VS Code extension that is based on the RISC-V extension. You only need this extension…

The semiconductor industry experts shared their perspectives on hiring and upskilling the VLSI engineers in this insightful panel discussion organized by Maven Silicon. In this…

Read the full announcement. OVER ONE HUNDRED ENGINEERS TO BE HIRED IN MULTIPLE LOCATIONS Codasip, the leading supplier of customizable RISC-V processor IP, announced today…

We are delighted to announce that several specifications have been opened to public review. All of these specifications add functionality to the RISC-V Privileged Specification.…

We continue to participate in the promising RISC-V ecosystem. Already in 2021, Ben Dooks fixed a challenging kernel bug, Robin Heywood prototyped an Arduino Mini…

When choosing a processor for space computing, there are many factors that come into play: because of the rigors of a harsh environment, developers must…

New CoreScore World Record Crams 6,000 SERV RISC-V Cores Into a Single FPGA | Gareth Halfacree, Hackster.io

New CoreScore World Record Crams 6,000 SERV RISC-V Cores Into a Single FPGA | Gareth Halfacree, Hackster.ioA single high-end Xilinx FPGA has played host to an impressive 6,000 individual SERV cores — a new CoreScore world record. There's a new world…

Studying RISC-V architecture to create customized systems for space computing | Leah Russell, University of Pittsburgh

Studying RISC-V architecture to create customized systems for space computing | Leah Russell, University of PittsburghWhen choosing a processor for space computing, there are many factors that come into play: because of the rigors of a harsh environment, developers must…

EdgeQ Samples 5G Basestation-on-a-Chip | Sally Ward-Foxton, EE Times

EdgeQ Samples 5G Basestation-on-a-Chip | Sally Ward-Foxton, EE TimesEdgeQ, the startup making basestation-on-a-chip silicon and software for 5G deployments, is now sampling its chip and phy software. The company has also released a…

EPI EPAC1.0 RISC-V Test Chip Samples Delivered | European Processor Initiative

EPI EPAC1.0 RISC-V Test Chip Samples Delivered | European Processor InitiativeAnother step closer to demonstrate the capabilities of a RISC-V based European microprocessor. The European Processor Initiative (EPI) https://www.european-processor-initiative.eu/, a project with 28 partners from…

Global alliance formed to promote open hardware support for women and underrepresented individuals | Aimee Kalnoskas, EE World Online

Global alliance formed to promote open hardware support for women and underrepresented individuals | Aimee Kalnoskas, EE World OnlineRISC-V International, a global open hardware standards organization, today announced the launch of the Open Hardware Diversity Alliance. The global Alliance, created by CHIPS Alliance,…

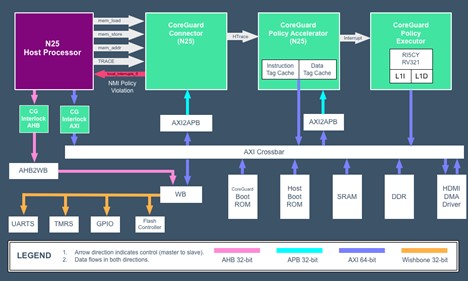

Building security into an AI SoC using CPU features with extensions | Marco Ciaffi, John Min, Embedded

Building security into an AI SoC using CPU features with extensions | Marco Ciaffi, John Min, EmbeddedWith the rapid deployment of artificial intelligence (AI), the focus of AI system on chip (SoC) design has been on building smarter, faster and cheaper…

ESP32-C6 WiFI 6 and Bluetooth 5 LE RISC-V SoC for IoT devices coming soon | JEAN-LUC AUFRANC (CNXSOFT)

ESP32-C6 WiFI 6 and Bluetooth 5 LE RISC-V SoC for IoT devices coming soon | JEAN-LUC AUFRANC (CNXSOFT)Espressif Systems introduced their first RISC-V wireless SoC last year with ESP32-C3 single-core 32-bit RISC-V SoC offering both 2.4GHz WiFi 4 and Bluetooth 5.0 LE…

New Part Day: Espressif Esp32-C6 Includes Wifi 6 and a RISC-V Core | Kerry Scharfglass, Hackaday

New Part Day: Espressif Esp32-C6 Includes Wifi 6 and a RISC-V Core | Kerry Scharfglass, HackadayIf you’re a reader of Hackaday, then you’ve almost certainly encountered an Espressif part. The twin microcontroller families ESP8266 and ESP32 burst onto the scene…

Video: Pipelining of RISC-V processor

Video: Pipelining of RISC-V processorThis is a short discussion of the concept of "pipelining" of RISC-V processor. It was created to supplement the lectures of a course focused on…

Video: Stall vs. Flush in RISC-V processor

Video: Stall vs. Flush in RISC-V processorThis is a short discussion of the concept of "pipelining" of RISC-V processor. It was created to supplement the lectures of a course focused on…

Xen releases a new version 4.15 after a slightly delayed development process | Simon Sharwood, APAC Editor, The Register

Xen releases a new version 4.15 after a slightly delayed development process | Simon Sharwood, APAC Editor, The RegisterThe Xen project has released another upgrade to its open source hypervisor. Development of this new cut – version 4.15 – proved a little trickier…

Open Source Leader Shares the Importance of Knowing and Embracing Your Strengths with Executive Kim McMahon | The Digital Executive

Open Source Leader Shares the Importance of Knowing and Embracing Your Strengths with Executive Kim McMahon | The Digital ExecutiveRISC-V International's Director of Visibility & Community Engagement, Kim McMahon, joins Coruzant Technologies for the Digital Executive podcast. She shares that you have to really…

RISC-V Star Rises Among Chip Developers Worldwide | Jeremy Hsu, IEEE Spectrum

RISC-V Star Rises Among Chip Developers Worldwide | Jeremy Hsu, IEEE SpectrumThe upstart RISC-V chip architecture has found international traction with its customizable open-source design and lack of licensing fees Read the full article.

Titanium Product Line Expands to 1M Logic Elements SANTA CLARA, Calif.--(BUSINESS WIRE)--Efinix®, an innovator in programmable product platforms and technology, today announced the expansion of…

Get Ready for the Most Interesting CPU Market We’ve Seen in Decades | Joel Hruska , Extreme Tech

Get Ready for the Most Interesting CPU Market We’ve Seen in Decades | Joel Hruska , Extreme TechFor most of the last 2.5 decades, the PC CPU industry has been dominated by a single architecture: x86. While the 1990s opened with a…

Standards CHIPS Alliance and RISC-V International will work jointly to update the OmniXtend Cache Coherency specification. The two groups formed a new OmniXtend working group…

DARPA adds RISC-V to its Toolbox: Defense researchers can get special access to SiFive chip designs | Katyanna Quach

DARPA adds RISC-V to its Toolbox: Defense researchers can get special access to SiFive chip designs | Katyanna QuachEngineers and scientists working on American military research programs can now access RISC-V processor core designs and associated blueprints through DARPA's Toolbox, and use the…