Intel® Pathfinder for RISC-V* is announcing an exciting array of new features to be released on December 12, 2022, while continuing to grow a healthy…

I am delighted to share my technical insights into RISC-V in this article to inspire and prepare the next generation of chip designers for the…

RISC-V Summit 2022: Future Careers Start Here

RISC-V Summit 2022: Future Careers Start HereRecent technology sector headlines have focused on companies implementing hiring freezes and layoffs – but the RISC-V ecosystem tells a different story: one of growth…

RISC-V Summit 2022: A Journey from Android to Outer Space … and Much More | RISC-V International

RISC-V Summit 2022: A Journey from Android to Outer Space … and Much More | RISC-V International2022 has been an incredible year for RISC-V, the open-standard Instruction Set Architecture (ISA) that is unleashing a new wave of innovation in computing. With…

2022 RISC-V Summit Technical Tutorials Announced | RISC-V International

2022 RISC-V Summit Technical Tutorials Announced | RISC-V InternationalThis past month, the RISC-V Summit 2022 schedule was announced. The Summit, which will be held on December 12-14, 2022, is the industry’s leading RISC-V…

XuanTie C908: High-performance RISC-V Processor Catered to AIoT Industry | Chang Liu, Alibaba Cloud

XuanTie C908: High-performance RISC-V Processor Catered to AIoT Industry | Chang Liu, Alibaba CloudXuanTie C908 is the latest RISC-V processor of the XuanTie series launched by T-Head Semiconductor. It has adopted the RV64GCB instruction and is compatible with…

Registration for the In-person RVfpga Session at the 2022 RISC-V Summit is Open. Space is Limited! | Imagination Technologies

Registration for the In-person RVfpga Session at the 2022 RISC-V Summit is Open. Space is Limited! | Imagination TechnologiesOnline is convenient and it has saved us during the pandemic, but you can’t beat in-person class! That immersive feeling of hands-on and the shared…

InspireSemi to Ring the Toronto Stock Exchange Closing Bell on October 25 | InspireSemi

InspireSemi to Ring the Toronto Stock Exchange Closing Bell on October 25 | InspireSemiVANCOUVER, British Columbia and AUSTIN, Texas, Oct. 24, 2022 (GLOBE NEWSWIRE) -- Inspire Semiconductor Holdings Inc. (TSXV: INSP) (“InspireSemi™” or the “Company”), a chip design company with…

First Patches from Alibaba Cloud Enable Android Open Source Project on RISC-V | Han Mao and David Chen, Alibaba Cloud

First Patches from Alibaba Cloud Enable Android Open Source Project on RISC-V | Han Mao and David Chen, Alibaba CloudThe Android Open Source Project (AOSP), an initiative by Google to guide development of the Android platform, has approved and merged patches from Alibaba Cloud.…

RISC-V Celebrates Upstreaming of Android Open Source Project RISC-V Port | RISC-V International

RISC-V Celebrates Upstreaming of Android Open Source Project RISC-V Port | RISC-V InternationalSuccess in the mobile and consumer device market depends on a vibrant software ecosystem. Over the past decade the Android Open Source Project (AOSP) has…

As a Strategic member of RISC-V International, Tiempo Secure will secure and integrate processors implementing the RISC-V open standard instruction set architecture (ISA) into its TESIC Secure Element…

RiVAI Technologies Announced New Products in Their RISC-V Vector DSP IP Family: RiVAI V7 And RiVAI V9+ | RiVAI Technologies

RiVAI Technologies Announced New Products in Their RISC-V Vector DSP IP Family: RiVAI V7 And RiVAI V9+ | RiVAI TechnologiesRiVAI Technologies has recently launched two new high-performance RISC-V vector IP series products: RiVAI V7 and RiVAI V9+, both with a customized RVV extension optimizing…

Vancouver based software studio Cartesian Theatre Corp. and SiFive, Inc., the founder and leader in RISC-V computing, are excited to announce CT’s Helios music recommendation…

RISC-V has been a very popular choice for embedded processor designs. Western Digital’s existing SweRV Core family is among the highest performance, area optimized embedded…

How the Imagination RVfpga: Understanding Computer Architecture course is giving engineering under-grads real-world skills | Robert Owen, Imagination Technologies

How the Imagination RVfpga: Understanding Computer Architecture course is giving engineering under-grads real-world skills | Robert Owen, Imagination TechnologiesIf you were to take a look through the academic materials now available about RISC-V you will find a wealth of information around SoC creation,…

Open source toolchains are key to building collaborative ecosystems, welcoming to new approaches, opportunistic/focused innovations and niche use cases. The ASIC design domain, especially in…

With the high performance Alibaba T-Head XuanTie processor coming to market, we believe it will benefit the RISC-V industry to port RISCV to the Android…

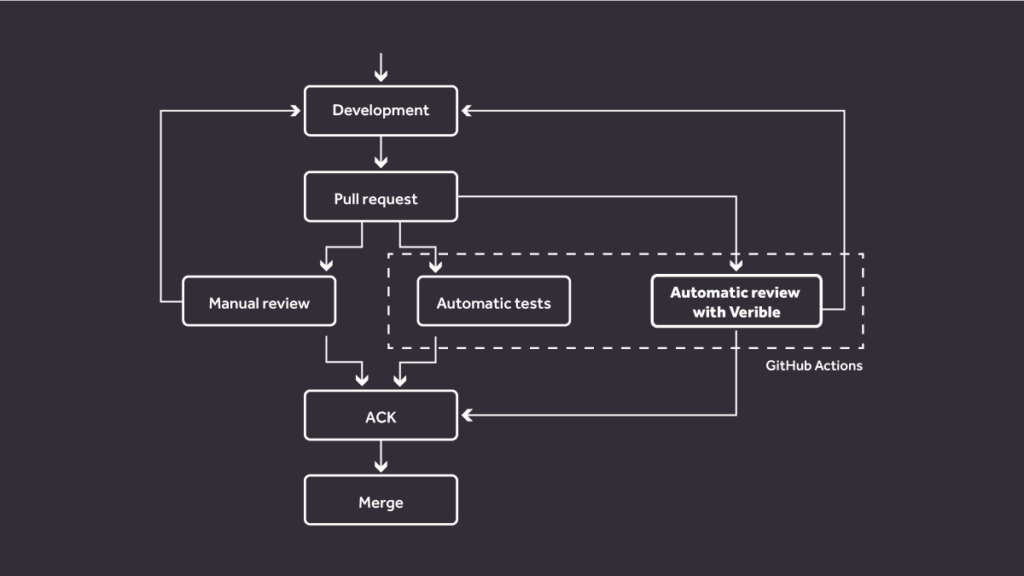

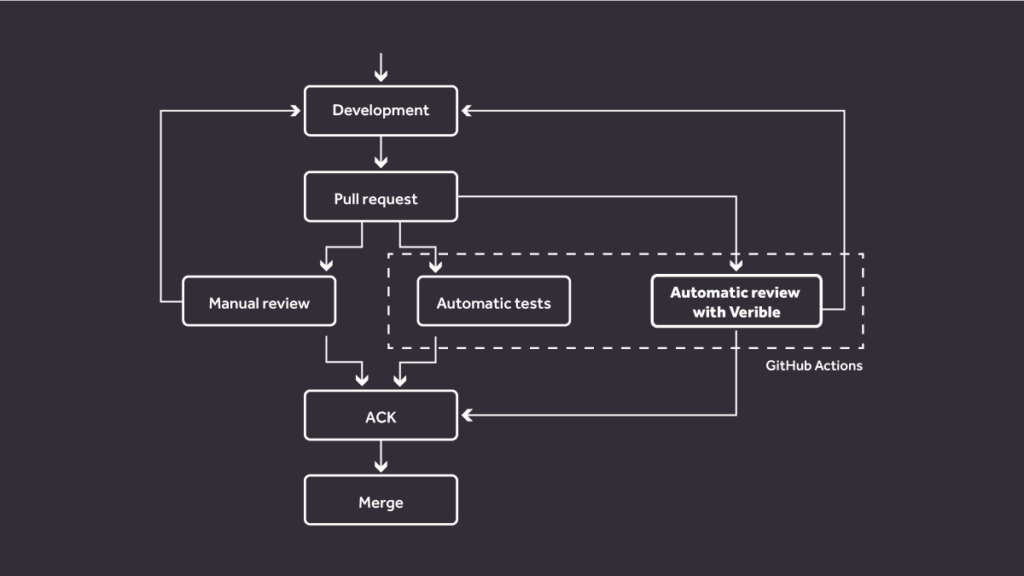

Automatic SystemVerilog linting in GitHub Actions with Verible | Antmicro

Automatic SystemVerilog linting in GitHub Actions with Verible | AntmicroWith the recent advances in open source ASIC development tools such as Verible, it has become easier to automate tasks and boost developer productivity. The Verible linter…

RISC-V RV32I I-Type | Maven Silicon

RISC-V RV32I I-Type | Maven SiliconThis video explains the RV32I I-Type instructions. RISC-V is growing rapidly, follow this RISC-V video blog series to obtain knowledge about RISC-V processors, Instruction formats,…

We recently held our fall 2021 CHIPS Alliance workshop with nearly 160 attendees present for informative seminars covering a range of topics including porting Android…

De-RISC – The H2020 Project Which Will Create The First RISC-V Fully European Platform For Aerospace, Celebrates Its Second Anniversary | Ana Rísquez Navarro, De-RISC

De-RISC – The H2020 Project Which Will Create The First RISC-V Fully European Platform For Aerospace, Celebrates Its Second Anniversary | Ana Rísquez Navarro, De-RISCThe De-RISC Project celebrates its second year through the introduction of a market-ready hardware-software platform based on the RISC-V instruction set architecture (ISA), productizing a…

Cambridge, UK - October 06, 2021, ZAYA now offers Trusted Execution Environments for RISC-V Architecture. There are different security approaches for IoT Security, and one…

RISC-V Mentorship: Formal Verification of SweRV EL2 Processor | Shashank V.M.

RISC-V Mentorship: Formal Verification of SweRV EL2 Processor | Shashank V.M.Background I was in the final year of my undergraduate degree in Electronics and Communication Engineering when I learnt out about the RISC-V Mentorship program from the RISC-V…

RISC-V is so much more than just an ISA for processors. Because of the openness of RISC-V, we are seeing an increase in innovation around…

Vancouver based software studio Cartesian Theatre Corp. and SiFive, Inc., the founder and leader in RISC-V computing, are excited to announce CT’s Helios music recommendation…

RISC-V has been a very popular choice for embedded processor designs. Western Digital’s existing SweRV Core family is among the highest performance, area optimized embedded…

How the Imagination RVfpga: Understanding Computer Architecture course is giving engineering under-grads real-world skills | Robert Owen, Imagination Technologies

How the Imagination RVfpga: Understanding Computer Architecture course is giving engineering under-grads real-world skills | Robert Owen, Imagination TechnologiesIf you were to take a look through the academic materials now available about RISC-V you will find a wealth of information around SoC creation,…

Open source toolchains are key to building collaborative ecosystems, welcoming to new approaches, opportunistic/focused innovations and niche use cases. The ASIC design domain, especially in…

With the high performance Alibaba T-Head XuanTie processor coming to market, we believe it will benefit the RISC-V industry to port RISCV to the Android…

Automatic SystemVerilog linting in GitHub Actions with Verible | Antmicro

Automatic SystemVerilog linting in GitHub Actions with Verible | AntmicroWith the recent advances in open source ASIC development tools such as Verible, it has become easier to automate tasks and boost developer productivity. The Verible linter…

RISC-V RV32I I-Type | Maven Silicon

RISC-V RV32I I-Type | Maven SiliconThis video explains the RV32I I-Type instructions. RISC-V is growing rapidly, follow this RISC-V video blog series to obtain knowledge about RISC-V processors, Instruction formats,…

We recently held our fall 2021 CHIPS Alliance workshop with nearly 160 attendees present for informative seminars covering a range of topics including porting Android…

De-RISC – The H2020 Project Which Will Create The First RISC-V Fully European Platform For Aerospace, Celebrates Its Second Anniversary | Ana Rísquez Navarro, De-RISC

De-RISC – The H2020 Project Which Will Create The First RISC-V Fully European Platform For Aerospace, Celebrates Its Second Anniversary | Ana Rísquez Navarro, De-RISCThe De-RISC Project celebrates its second year through the introduction of a market-ready hardware-software platform based on the RISC-V instruction set architecture (ISA), productizing a…

Cambridge, UK - October 06, 2021, ZAYA now offers Trusted Execution Environments for RISC-V Architecture. There are different security approaches for IoT Security, and one…

RISC-V Mentorship: Formal Verification of SweRV EL2 Processor | Shashank V.M.

RISC-V Mentorship: Formal Verification of SweRV EL2 Processor | Shashank V.M.Background I was in the final year of my undergraduate degree in Electronics and Communication Engineering when I learnt out about the RISC-V Mentorship program from the RISC-V…

RISC-V is so much more than just an ISA for processors. Because of the openness of RISC-V, we are seeing an increase in innovation around…