Production-Ready, Automotive-Grade, AI-Native: RISC-V at Embedded World 2026

Ahead of Embedded World, we explore what our members and co-exhibitors will showcase in Nuremberg, the common threads linking their work, and what this reveals about the embedded landscape in 2026.

Using a Performance Model to Implement a Superscalar CVA6

Using a Performance Model to Implement a Superscalar CVA6Project Snapshot How does performance modeling accelerate real hardware innovation in open RISC-V designs? In this paper, Thales demonstrates a performance model of the CVA6…

Production-Ready, Automotive-Grade, AI-Native: RISC-V at Embedded World 2026

Production-Ready, Automotive-Grade, AI-Native: RISC-V at Embedded World 2026Ahead of Embedded World, we explore what our members and co-exhibitors will showcase in Nuremberg, the common threads linking their work, and what this reveals…

Support RAJA and Scientific Applications on RVV Architectures

Support RAJA and Scientific Applications on RVV ArchitecturesProject Snapshot In this work, we aim to make RVV more accessible to scientific applications by integrating it into the RAJA performance-portability framework. RAJA is…

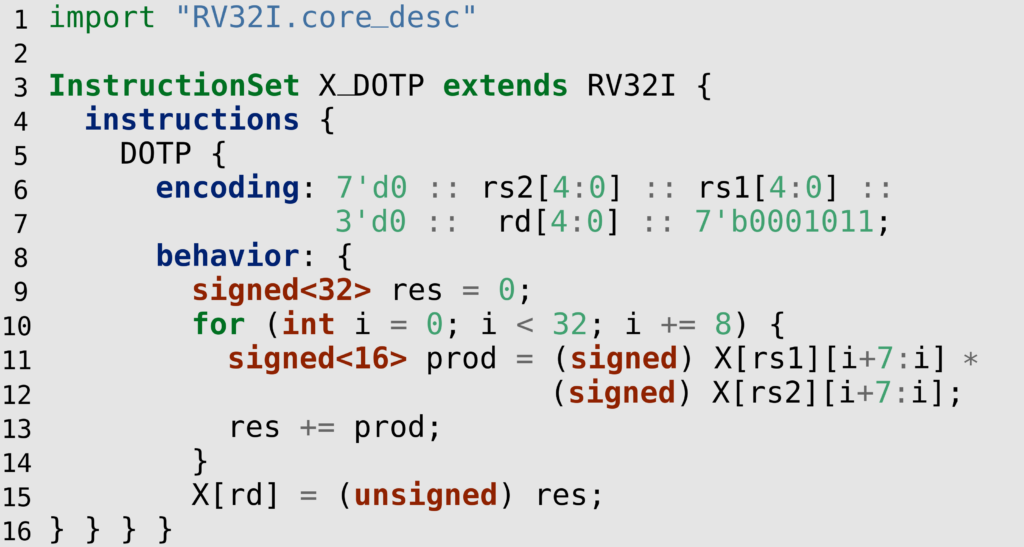

RISC-V Mentorship Taught Me the RISC-V ISA Is Far More Than a Reference Manual

RISC-V Mentorship Taught Me the RISC-V ISA Is Far More Than a Reference ManualDeveloper and RISC-V Mentee Animesh Agarwal talks us through what he learned during his time on placement at Ventana Micro, and how it changed how…

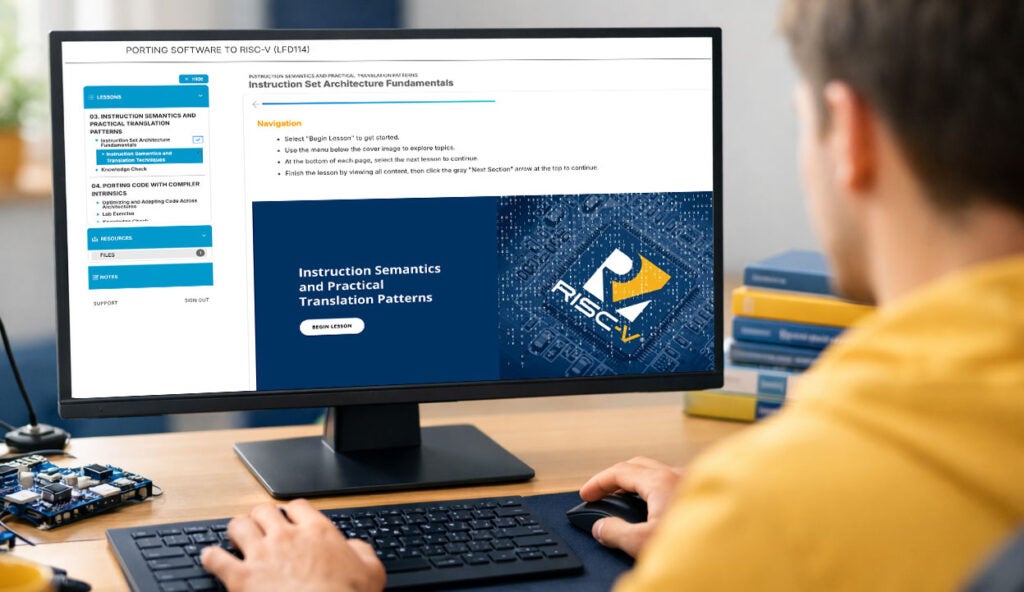

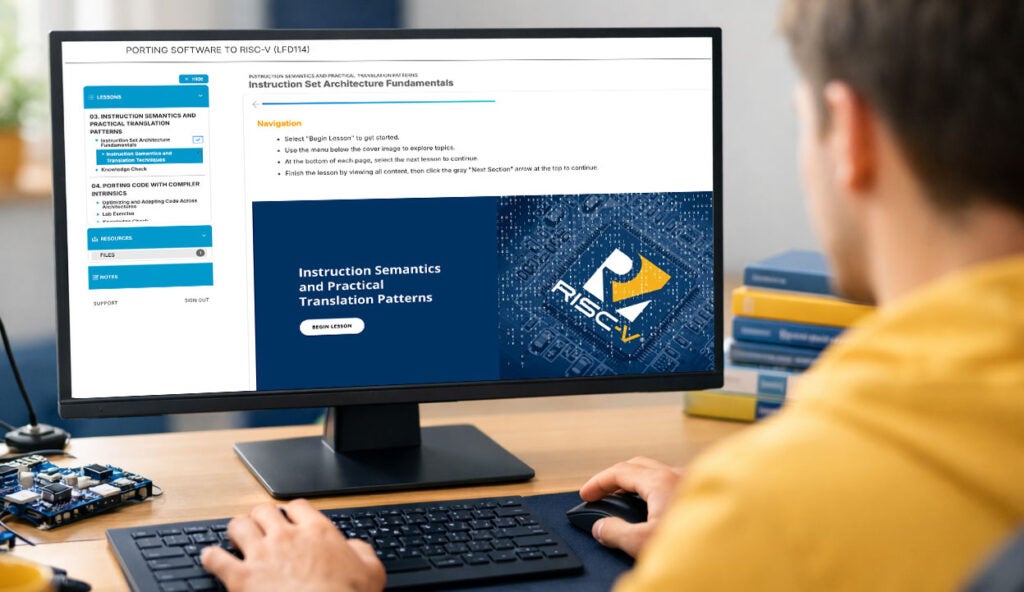

Start Porting Software To RISC-V Today With Our New, Free Online Course

Start Porting Software To RISC-V Today With Our New, Free Online CoursePorting Software to RISC-V (LFD114) is our free course for experienced engineers who need to move performance-critical software to RISC-V.

How We’re Using AI to Streamline RISC-V Regression Debugging

How We’re Using AI to Streamline RISC-V Regression DebuggingAI verification startup Verifaix explains how its AI Debug Agent automates regression debugging, helping RISC-V developers reduce manual verification effort and accelerate design cycles.

One ISA, Infinite Use Cases: RISC-V and the Road to Workload-Specific Silicon

One ISA, Infinite Use Cases: RISC-V and the Road to Workload-Specific SiliconIn this blog, Krste Asanović explains why in 2026, the state of the RISC-V union isn't just strong: it's stronger than ever.

And the winners are… In September we sent out a call for proposals, looking for researchers and academics that would leverage AI to speed up…

Ocelot3: Full Vector “V” Extension for BOOM

Ocelot3: Full Vector “V” Extension for BOOMProject Snapshot Ocelot is an open-source project that enables vector support for the BOOM core. In this generation, we achieve full RVV 1.0 support. The…

The Final Verification Frontier: How Breker Battle-Hardened RISC-V for Space

The Final Verification Frontier: How Breker Battle-Hardened RISC-V for SpaceVerification company Breker is well-versed in ensuring complex semiconductors stay robust in tough conditions, but space forced it to think differently.

Notes From the 2025 RISC-V Industry Development Conference

Notes From the 2025 RISC-V Industry Development ConferenceI have just returned from the 2025 RISC-V Industry Development Conference, held across Zhuhai and Macau. Guided by the 2025 theme “Accelerating Standardization, Facilitating Connection”…

Enabling High Performance RISC-V Software for AI in the Real World

Enabling High Performance RISC-V Software for AI in the Real WorldEmbecosm used the oneAPI Construction Kit to explore accelerating PyTorch using RISC-V cores, trying over a thousand in emulation and some on an FPGA. This…

Production-Ready, Automotive-Grade, AI-Native: RISC-V at Embedded World 2026

Production-Ready, Automotive-Grade, AI-Native: RISC-V at Embedded World 2026Ahead of Embedded World, we explore what our members and co-exhibitors will showcase in Nuremberg, the common threads linking their work, and what this reveals…

Start Porting Software To RISC-V Today With Our New, Free Online Course

Start Porting Software To RISC-V Today With Our New, Free Online CoursePorting Software to RISC-V (LFD114) is our free course for experienced engineers who need to move performance-critical software to RISC-V.

Introducing the RISCstar Toolchain for RISC-V

Introducing the RISCstar Toolchain for RISC-VThe newly released RISCstar toolchain is a pre-compiled family of GNU toolchains for RISC-V developers. It supports the entire RISC-V ecosystem, from the latest 64-bit…

RISC-V Takes First Step Toward International Standardization as ISO/IEC JTC1 Grants PAS Submitter Status

RISC-V Takes First Step Toward International Standardization as ISO/IEC JTC1 Grants PAS Submitter StatusAt RISC-V Summit North America 2025, Andrea Gallo, CEO RISC-V International, and Phil Wennblom, Chair of the ISO/IEC Joint Technical Committee (JTC 1)., announced that…

Ashling and Embecosm Extend PyTorch AI to RISC-V Embedded Devices

Ashling and Embecosm Extend PyTorch AI to RISC-V Embedded DevicesAt RISC-V North American Summit in Santa Clara, Ashling and Embecosm today announced robust ExecuTorch implementations optimised for resource-constrained devices, including RISC-V based microcontrollers. The…

New Course Coming Soon: Porting Software to RISC-V (LFD 114)

New Course Coming Soon: Porting Software to RISC-V (LFD 114)The knowledge gap for porting software to RISC-V is about to close. RISCstar Solutions, in close collaboration with RISC-V International and the Linux Foundation, has…

Europe Achieves a Key Milestone with the Europe’s First Out-of-Order RISC-V Processor chip, with the eProcessor Project

Europe Achieves a Key Milestone with the Europe’s First Out-of-Order RISC-V Processor chip, with the eProcessor ProjectThe eProcessor Project today announced the successful development and deployment of the Europe’s first out-of-order RISC-V processor silicon. The processor, manufactured in a 22nm process,…

Risky Systems’ Bob Jones explains why the company’s latest core is set to revolutionize the AI SoC market, and how it intends to use it…

NASA, Google, AWS Join Stellar Line-up for RISC-V Summit North America 2025

NASA, Google, AWS Join Stellar Line-up for RISC-V Summit North America 2025RISC-V Summit North America 2025 will bring the global RISC-V community together in Santa Clara for two days of keynotes, technical sessions, workshops, and demos.

World RISC-V Days: Hanoi Vietnam 2025

World RISC-V Days: Hanoi Vietnam 2025Summary Under the theme “RISC-V: The Future of Open Hardware and Innovation,” the event brought together industry leaders, researchers, and tech enthusiasts for a full…

World RISC-V Days: Tokyo Japan 2025

World RISC-V Days: Tokyo Japan 2025Summary Despite a bit of rainy weather, the Tokyo RISC-V community came together at a local restaurant for a lively evening of conversation, networking, and…

World RISC-V Days: Bangalore India 2025

World RISC-V Days: Bangalore India 2025Summary A small but spirited crowd in Bangalore came together to dive into RISC-V’s future in the region—exploring RISC-V on FPGA, discussing where the local…

And the winners are… In September we sent out a call for proposals, looking for researchers and academics that would leverage AI to speed up…

A Hands-On Look at RISC-V Verification for Next-Gen Designs Using Synopsys’ Flow

A Hands-On Look at RISC-V Verification for Next-Gen Designs Using Synopsys’ FlowVerification is no mean feat. With new extensions, evolving specs, growing pressure for faster cycles, and a continuous flow of tool innovations, it constantly balances…

New to RISC-V? Here’s Why Summit 2025 is the Place to Begin Your Journey

New to RISC-V? Here’s Why Summit 2025 is the Place to Begin Your JourneyThe 2025 RISC-V Summit North America runs October 22–23 in Santa Clara, California, with a member day on October 21. If you are new to…

RISC-V: The AI-Native Platform for the Next Trillion Dollars of Compute

RISC-V: The AI-Native Platform for the Next Trillion Dollars of ComputeWe explore how companies across industries are proving the viability of RISC-V as a native architecture for modern AI workloads

Design Approaches and Architectures of RISC-V SoCs

Design Approaches and Architectures of RISC-V SoCsAuthor: P R Sivakumar, Founder and CEO, Maven Silicon We design different kinds of System-on-Chips (SoCs/Chips) tailored for different electronic products. Let’s explore how we…

From Simulation Bottlenecks to Formal Confidence: Leveraging Formal for Exhaustive RISC-V Verification

From Simulation Bottlenecks to Formal Confidence: Leveraging Formal for Exhaustive RISC-V VerificationIntroduction Various methods are used for design verification, including simulation, emulation, and formal verification. While simulation and emulation are effective at identifying bugs, they may…

Arteris’ Multi-Die Solution for the RISC-V Ecosystem

Arteris’ Multi-Die Solution for the RISC-V Ecosystemby Ashley Stevens, Director of Product Management and Marketing at Arteris The amount of compute used to train frontier AI models has been doubling roughly…

7 Critical Components of the Car of Tomorrow

7 Critical Components of the Car of TomorrowWith IAA Mobility and the RISC-V Automotive Conference 2025 just around the corner, I’ve pulled together the top themes from recent expert panels that every…

RISC-V Summit China 2025: Reflections from a RISC-V Software Contributor

RISC-V Summit China 2025: Reflections from a RISC-V Software ContributorBy Guodong Xu, Director China Operations, RISCstar Solutions The 2025 RISC-V Summit China reached an unprecedented level of excitement, drawing a record-breaking crowd of over…

Certifying Embedded Applications Running on PolarFire® SoC FPGAs

Certifying Embedded Applications Running on PolarFire® SoC FPGAsBy: Stephen Di Camillo, Technical Marketing and Business Development Manager Embedded system developers facing the increasingly complex challenge of certifying embedded applications running on complex…

Cost-Effective and Scalable: A Smarter Choice for RISC-V Development

Cost-Effective and Scalable: A Smarter Choice for RISC-V DevelopmentThe RISC-V ecosystem is witnessing remarkable growth, driven by increasing industry adoption and a thriving open-source community. As companies and developers seek customizable computing solutions,…

Using a Performance Model to Implement a Superscalar CVA6

Using a Performance Model to Implement a Superscalar CVA6Project Snapshot How does performance modeling accelerate real hardware innovation in open RISC-V designs? In this paper, Thales demonstrates a performance model of the CVA6…

Support RAJA and Scientific Applications on RVV Architectures

Support RAJA and Scientific Applications on RVV ArchitecturesProject Snapshot In this work, we aim to make RVV more accessible to scientific applications by integrating it into the RAJA performance-portability framework. RAJA is…

How We’re Using AI to Streamline RISC-V Regression Debugging

How We’re Using AI to Streamline RISC-V Regression DebuggingAI verification startup Verifaix explains how its AI Debug Agent automates regression debugging, helping RISC-V developers reduce manual verification effort and accelerate design cycles.

Ocelot3: Full Vector “V” Extension for BOOM

Ocelot3: Full Vector “V” Extension for BOOMProject Snapshot Ocelot is an open-source project that enables vector support for the BOOM core. In this generation, we achieve full RVV 1.0 support. The…

Enabling High Performance RISC-V Software for AI in the Real World

Enabling High Performance RISC-V Software for AI in the Real WorldEmbecosm used the oneAPI Construction Kit to explore accelerating PyTorch using RISC-V cores, trying over a thousand in emulation and some on an FPGA. This…

Optimizing Hardware for Neural Network Inference using Virtual Prototypes

Optimizing Hardware for Neural Network Inference using Virtual PrototypesProject Snapshot Identifying the optimal hardware configuration for running NN inference on edge devices is critical for maximizing performance. Tailoring HW designs to specific applications…

A RISC-V Based Accelerator for Post Quantum Cryptography

A RISC-V Based Accelerator for Post Quantum CryptographyProject Snapshot Post-Quantum Cryptography (PQC) is a topic of increased interest in the past decade, both with regards to the cryptosystem definition and the hardware…

CVA6 RISC-V PMP Vulnerabilities against FIA

CVA6 RISC-V PMP Vulnerabilities against FIAProject Snapshot Fault Injection Attacks (FIA) present considerable threats to the security and reliability of embedded systems. FIAs can compromise an embedded processor by altering…

Learning Computer Architecture with a Visual Simulation of RISC-V Processors

Learning Computer Architecture with a Visual Simulation of RISC-V ProcessorsProject Snapshot This work presents an interactive way of teaching computer architecture using Logisim Evolution, enabling students to construct and debug single-cycle and pipelined CPUs.…

TYRCA: A RISC-V Tightly-Coupled Accelerator For Code-Based Cryptography

TYRCA: A RISC-V Tightly-Coupled Accelerator For Code-Based CryptographyProject Snapshot Post-quantum cryptography (PQC) has garnered significant attention across various communities, particularly with the National Institute of Standards and Technology (NIST) advancing to the…

HaDes-V – Learning by Puzzling: A Modular Approach to RISC-V Processor Design Education

HaDes-V – Learning by Puzzling: A Modular Approach to RISC-V Processor Design EducationProject Snapshot HaDes-V is an Open Educational Resource for learning microcontroller design. It guides through creating a 5-stage pipelined 32-bit RISC-V processor using SystemVerilog and…

Simplifying Sail Simulations and Architectural Compatibility Testing

Simplifying Sail Simulations and Architectural Compatibility TestingGreg Sterling from RISC-V International has worked with Carl Perry to create a RISC-V development container to help streamline the process of working with RISC-V…

And the winners are… In September we sent out a call for proposals, looking for researchers and academics that would leverage AI to speed up…

A Hands-On Look at RISC-V Verification for Next-Gen Designs Using Synopsys’ Flow

A Hands-On Look at RISC-V Verification for Next-Gen Designs Using Synopsys’ FlowVerification is no mean feat. With new extensions, evolving specs, growing pressure for faster cycles, and a continuous flow of tool innovations, it constantly balances…

New to RISC-V? Here’s Why Summit 2025 is the Place to Begin Your Journey

New to RISC-V? Here’s Why Summit 2025 is the Place to Begin Your JourneyThe 2025 RISC-V Summit North America runs October 22–23 in Santa Clara, California, with a member day on October 21. If you are new to…

RISC-V: The AI-Native Platform for the Next Trillion Dollars of Compute

RISC-V: The AI-Native Platform for the Next Trillion Dollars of ComputeWe explore how companies across industries are proving the viability of RISC-V as a native architecture for modern AI workloads

Design Approaches and Architectures of RISC-V SoCs

Design Approaches and Architectures of RISC-V SoCsAuthor: P R Sivakumar, Founder and CEO, Maven Silicon We design different kinds of System-on-Chips (SoCs/Chips) tailored for different electronic products. Let’s explore how we…

From Simulation Bottlenecks to Formal Confidence: Leveraging Formal for Exhaustive RISC-V Verification

From Simulation Bottlenecks to Formal Confidence: Leveraging Formal for Exhaustive RISC-V VerificationIntroduction Various methods are used for design verification, including simulation, emulation, and formal verification. While simulation and emulation are effective at identifying bugs, they may…

Arteris’ Multi-Die Solution for the RISC-V Ecosystem

Arteris’ Multi-Die Solution for the RISC-V Ecosystemby Ashley Stevens, Director of Product Management and Marketing at Arteris The amount of compute used to train frontier AI models has been doubling roughly…

7 Critical Components of the Car of Tomorrow

7 Critical Components of the Car of TomorrowWith IAA Mobility and the RISC-V Automotive Conference 2025 just around the corner, I’ve pulled together the top themes from recent expert panels that every…

RISC-V Summit China 2025: Reflections from a RISC-V Software Contributor

RISC-V Summit China 2025: Reflections from a RISC-V Software ContributorBy Guodong Xu, Director China Operations, RISCstar Solutions The 2025 RISC-V Summit China reached an unprecedented level of excitement, drawing a record-breaking crowd of over…

Certifying Embedded Applications Running on PolarFire® SoC FPGAs

Certifying Embedded Applications Running on PolarFire® SoC FPGAsBy: Stephen Di Camillo, Technical Marketing and Business Development Manager Embedded system developers facing the increasingly complex challenge of certifying embedded applications running on complex…

Cost-Effective and Scalable: A Smarter Choice for RISC-V Development

Cost-Effective and Scalable: A Smarter Choice for RISC-V DevelopmentThe RISC-V ecosystem is witnessing remarkable growth, driven by increasing industry adoption and a thriving open-source community. As companies and developers seek customizable computing solutions,…