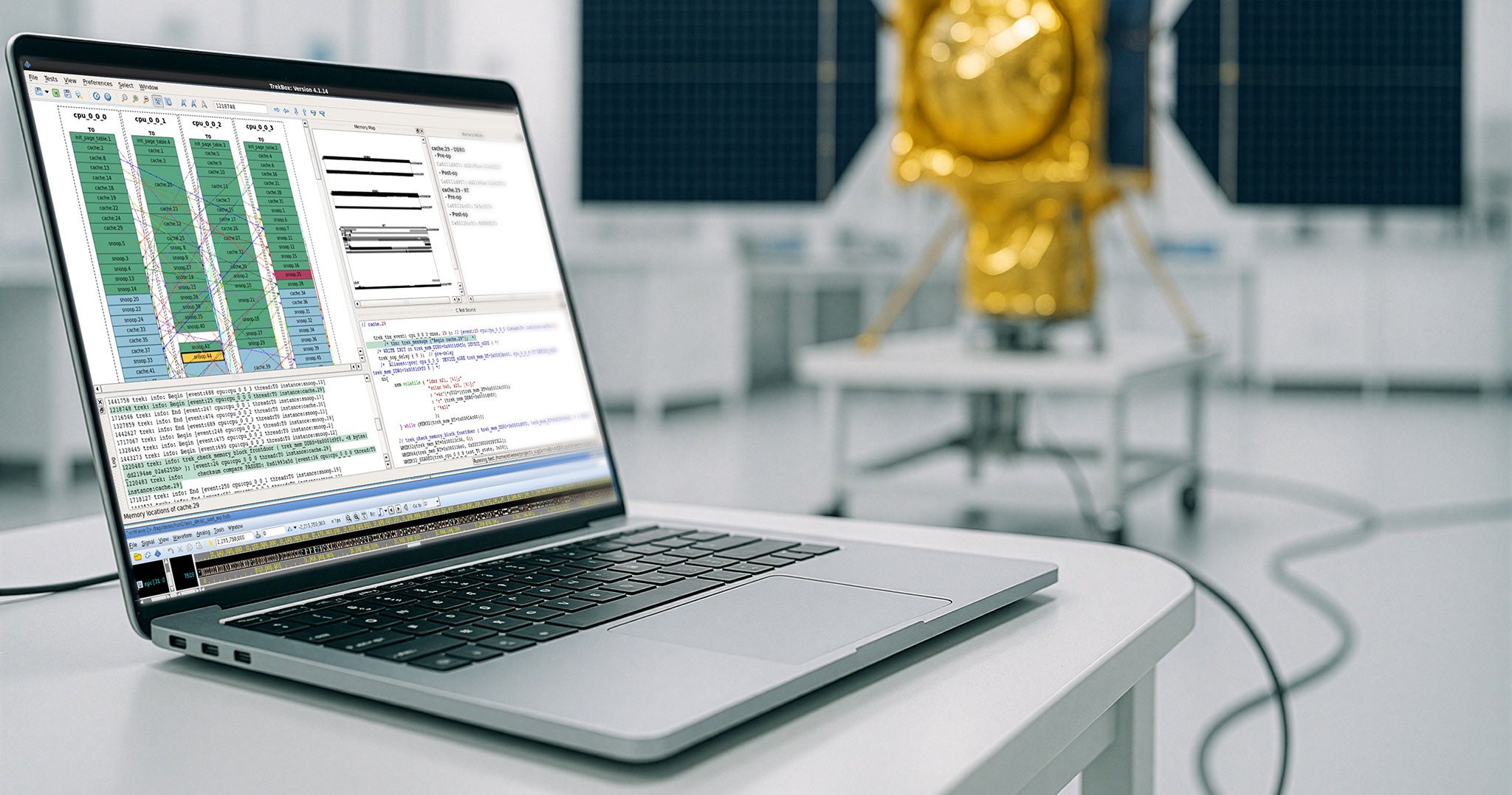

The Final Verification Frontier: How Breker Battle-Hardened RISC-V for Space

Verification company Breker is well-versed in ensuring complex semiconductors stay robust in tough conditions, but space forced it to think differently.

RISC-V: The AI-Native Platform for the Next Trillion Dollars of Compute

RISC-V: The AI-Native Platform for the Next Trillion Dollars of ComputeWe explore how companies across industries are proving the viability of RISC-V as a native architecture for modern AI workloads

Design Approaches and Architectures of RISC-V SoCs

Design Approaches and Architectures of RISC-V SoCsAuthor: P R Sivakumar, Founder and CEO, Maven Silicon We design different kinds of System-on-Chips (SoCs/Chips) tailored for different electronic products. Let’s explore how we…

From Simulation Bottlenecks to Formal Confidence: Leveraging Formal for Exhaustive RISC-V Verification

From Simulation Bottlenecks to Formal Confidence: Leveraging Formal for Exhaustive RISC-V VerificationIntroduction Various methods are used for design verification, including simulation, emulation, and formal verification. While simulation and emulation are effective at identifying bugs, they may…

Arteris’ Multi-Die Solution for the RISC-V Ecosystem

Arteris’ Multi-Die Solution for the RISC-V Ecosystemby Ashley Stevens, Director of Product Management and Marketing at Arteris The amount of compute used to train frontier AI models has been doubling roughly…

CVA6 RISC-V PMP Vulnerabilities against FIA

CVA6 RISC-V PMP Vulnerabilities against FIAProject Snapshot Fault Injection Attacks (FIA) present considerable threats to the security and reliability of embedded systems. FIAs can compromise an embedded processor by altering…

World RISC-V Days: Hanoi Vietnam 2025

World RISC-V Days: Hanoi Vietnam 2025Summary Under the theme “RISC-V: The Future of Open Hardware and Innovation,” the event brought together industry leaders, researchers, and tech enthusiasts for a full…

World RISC-V Days: Tokyo Japan 2025

World RISC-V Days: Tokyo Japan 2025Summary Despite a bit of rainy weather, the Tokyo RISC-V community came together at a local restaurant for a lively evening of conversation, networking, and…

World RISC-V Days: Bangalore India 2025

World RISC-V Days: Bangalore India 2025Summary A small but spirited crowd in Bangalore came together to dive into RISC-V’s future in the region—exploring RISC-V on FPGA, discussing where the local…

World RISC-V Days: Beijing 2025

World RISC-V Days: Beijing 2025Summary World RISC-V Day Beijing brought the community together for a high-energy, high-impact celebration of open computing. With 200+ attendees onsite and 5,400+ participants joining…

World RISC-V Days: Hong Kong China 2025

World RISC-V Days: Hong Kong China 2025Summary World RISC-V Day Hong Kong, hosted by ExpressVPN, was a standout moment in this year’s global celebrations. As the DeepComputing team traveled across Asia to…

World RISC-V Days: Karachi Pakistan 2025

World RISC-V Days: Karachi Pakistan 2025Summary Dr. Farhan Ahmed Karim kicked off World RISC-V Day in Karachi with a powerful keynote, “Empowering Nations with RISC-V – A Path to Tech…

World RISC-V Days: Lahore Pakistan 2025

World RISC-V Days: Lahore Pakistan 2025Summary The event delivered a full, fast-paced program packed with poster sessions, networking, and hands-on challenges. Highlights included talks like “RISC-V Uncore IPs: An Introduction…

RISC-V International Newsletter – December 2024

RISC-V International Newsletter – December 2024Message from RISC-V International As we reflect on 2024, we wanted to express our heartfelt gratitude to the entire RISC-V ecosystem. This year has been…

RISC-V CEO Calista Redmond resigns after 5+ years of progress

RISC-V CEO Calista Redmond resigns after 5+ years of progressBy: Calista Redmond | CEO, RISC-V International It is with deep gratitude that I announce my resignation from RISC-V International as I’ve accepted a new…

RISC-V Announces Ratification of the RVA23 Profile Standard

RISC-V Announces Ratification of the RVA23 Profile StandardVector and Hypervisor extensions are key mandatory components of the RVA23 Profile, addressing math-intensive workloads including AI/ML & cryptography, and enterprise hardware, operating systems and…

RISC-V International Newsletter – September 2024

RISC-V International Newsletter – September 2024Message from RISC-V International The countdown is on! RISC-V Summit North America takes place on October 22-23 at the Santa Clara Convention Center. The Summit is…

RISC-V International Names Andrea Gallo as VP, Technology

RISC-V International Names Andrea Gallo as VP, TechnologyIndustry Veteran Brings Software and Hardware Experience to Role Guiding all RISC-V Technical Activities MUNICH, Germany – June 24, 2024 – RISC-V International, the global…

RISC-V International Newsletter – June 2024

RISC-V International Newsletter – June 2024Message from RISC-V International Events are key to the success of RISC-V, where we come together to share the latest developments and build the relationships…

MEDIA ALERT: Calista Redmond, CEO of RISC-V International, to Speak at ESD Alliance 2024 CEO Executive Outlook WHO: Calista Redmond, CEO of RISC-V International WHAT:…

RISC-V International Achieves Milestone with Ratification of 40 Specifications in Two Years

RISC-V International Achieves Milestone with Ratification of 40 Specifications in Two YearsLatest Ratifications Primarily Target Core Areas of Efficiency, Vector, and Virtualization ZURICH – April 4, 2024 – RISC-V International, the global standards organization, today announced…

RISC-V International to Showcase the Latest RISC-V Developments at embedded world 2024

RISC-V International to Showcase the Latest RISC-V Developments at embedded world 2024WHO: RISC-V International WHAT: RISC-V International will be exhibiting at embedded world 2024, sharing the latest developments from its community and showcasing a range of…

Message from RISC-V International 2024 is now well underway and we have some exciting new developments from our members worldwide! RISC-V is truly a global…

Message from RISC-V International As we look back on 2023, we wanted to express our gratitude to the entire RISC-V ecosystem. Throughout the year, we…

Exploring RISC-V ISA Developments and Technical Highlights from 2024

Exploring RISC-V ISA Developments and Technical Highlights from 20242024 has been a year of great technical progress for the RISC-V ISA. Our 75 Committees and Groups, staffed by contributors from RISC-V member organizations…

RISC-V 2024: A Year of Global Growth and Innovation

RISC-V 2024: A Year of Global Growth and InnovationAs 2024 comes to a close, it’s clear that this has been a transformative year for RISC-V. From achieving industry firsts to driving innovation across…

S2C Launches Prodigy S8-100 Series: 100M Gate FPGA Prototyping for AI and HPC

S2C Launches Prodigy S8-100 Series: 100M Gate FPGA Prototyping for AI and HPCS2C Launches Prodigy S8-100 Series: 100M Gate FPGA Prototyping for AI and HPC December 19, 2024 – S2C, a global leader in FPGA-based prototyping solutions,…

My Journey with the RISC-V Mentorship | Sailing Downstream II

My Journey with the RISC-V Mentorship | Sailing Downstream IIby Linda Njau, RISC-V Mentee at Ventana Micro SystemsI came across the Linux/RISC-V mentorship while searching for an internship, and my curiosity was sparked by…

XuanTie Co-Processor Interface Solution: A Bridge to Efficient Collaborative Computing

XuanTie Co-Processor Interface Solution: A Bridge to Efficient Collaborative ComputingWeitong Su, Alibaba DAMO Academy Co-processors are specialized units designed to assist the main processor in executing specific tasks, such as graphics processing and signal…

Enhancing the Future of AI/ML with Attached Matrix Extension

Enhancing the Future of AI/ML with Attached Matrix ExtensionZhao Jiang, Alibaba DAMO Academy In recent years, the rapid advancement of AI technologies, particularly deep learning, has significantly increased the demand for computing power,…

Meet Andrea Gallo, RVFA: A Senior IT Leader’s Career Pivot

Meet Andrea Gallo, RVFA: A Senior IT Leader’s Career PivotAndrea Gallo, RVFA Vice President of Technology at RISC-V InternationalAfter decades of a highly successful, Arm-focused career, Andrea Gallo was ready to take his professional…

Triton kernel performance on RISC-V CPU

Triton kernel performance on RISC-V CPUIntroduction to Triton Triton is an open-source, Python-based Domain-Specific Language (DSL) developed by OpenAI to simplify the writing of high-performance GPGPU code. It was first…

Stream Computing Provides Smart Community Services Based on RISC-V Computing Power and LLMs

Stream Computing Provides Smart Community Services Based on RISC-V Computing Power and LLMsBy Deke Wang and David Chen, Stream Computing In the wave of digital transformation, the intelligent upgrade of community services has become key to improving…

Stream Computing RISC-V Matrix Extension Open Source Project Upgrades to Version 0.5, Supporting Vector+Matrix Implementation

Stream Computing RISC-V Matrix Extension Open Source Project Upgrades to Version 0.5, Supporting Vector+Matrix ImplementationBy Fujie Fan and David Chen, Stream Computing Background: In order to solve the problem of instruction fragmentation of RISC-V in AI field and accelerate…

Real-Time, Zero-Trust Cybersecurity for the PolarFire® SoC and IoT

Real-Time, Zero-Trust Cybersecurity for the PolarFire® SoC and IoTDOME Cybersecurity provides a flexible Software Development Kit (SDK) for connecting the PolarFire FPGA to the IoT By: Harry Ostaffe Vice President, Marketing @ Veridify…

RISC-V Forum Shenzhen: Unleashing Power of Electronics Making to Lead Global Open-Source Innovations

RISC-V Forum Shenzhen: Unleashing Power of Electronics Making to Lead Global Open-Source InnovationsOn October 17, the inaugural RISC-V Eco-system Development Forum, held as part of the Guangdong-Hong Kong-Macao Greater Bay Area Semiconductor Industry Expo, took place at…

Exploring RISC-V ISA Developments and Technical Highlights from 2024

Exploring RISC-V ISA Developments and Technical Highlights from 20242024 has been a year of great technical progress for the RISC-V ISA. Our 75 Committees and Groups, staffed by contributors from RISC-V member organizations…

RISC-V 2024: A Year of Global Growth and Innovation

RISC-V 2024: A Year of Global Growth and InnovationAs 2024 comes to a close, it’s clear that this has been a transformative year for RISC-V. From achieving industry firsts to driving innovation across…

S2C Launches Prodigy S8-100 Series: 100M Gate FPGA Prototyping for AI and HPC

S2C Launches Prodigy S8-100 Series: 100M Gate FPGA Prototyping for AI and HPCS2C Launches Prodigy S8-100 Series: 100M Gate FPGA Prototyping for AI and HPC December 19, 2024 – S2C, a global leader in FPGA-based prototyping solutions,…

My Journey with the RISC-V Mentorship | Sailing Downstream II

My Journey with the RISC-V Mentorship | Sailing Downstream IIby Linda Njau, RISC-V Mentee at Ventana Micro SystemsI came across the Linux/RISC-V mentorship while searching for an internship, and my curiosity was sparked by…

XuanTie Co-Processor Interface Solution: A Bridge to Efficient Collaborative Computing

XuanTie Co-Processor Interface Solution: A Bridge to Efficient Collaborative ComputingWeitong Su, Alibaba DAMO Academy Co-processors are specialized units designed to assist the main processor in executing specific tasks, such as graphics processing and signal…

Enhancing the Future of AI/ML with Attached Matrix Extension

Enhancing the Future of AI/ML with Attached Matrix ExtensionZhao Jiang, Alibaba DAMO Academy In recent years, the rapid advancement of AI technologies, particularly deep learning, has significantly increased the demand for computing power,…

Meet Andrea Gallo, RVFA: A Senior IT Leader’s Career Pivot

Meet Andrea Gallo, RVFA: A Senior IT Leader’s Career PivotAndrea Gallo, RVFA Vice President of Technology at RISC-V InternationalAfter decades of a highly successful, Arm-focused career, Andrea Gallo was ready to take his professional…

Triton kernel performance on RISC-V CPU

Triton kernel performance on RISC-V CPUIntroduction to Triton Triton is an open-source, Python-based Domain-Specific Language (DSL) developed by OpenAI to simplify the writing of high-performance GPGPU code. It was first…

Stream Computing Provides Smart Community Services Based on RISC-V Computing Power and LLMs

Stream Computing Provides Smart Community Services Based on RISC-V Computing Power and LLMsBy Deke Wang and David Chen, Stream Computing In the wave of digital transformation, the intelligent upgrade of community services has become key to improving…

Stream Computing RISC-V Matrix Extension Open Source Project Upgrades to Version 0.5, Supporting Vector+Matrix Implementation

Stream Computing RISC-V Matrix Extension Open Source Project Upgrades to Version 0.5, Supporting Vector+Matrix ImplementationBy Fujie Fan and David Chen, Stream Computing Background: In order to solve the problem of instruction fragmentation of RISC-V in AI field and accelerate…

Real-Time, Zero-Trust Cybersecurity for the PolarFire® SoC and IoT

Real-Time, Zero-Trust Cybersecurity for the PolarFire® SoC and IoTDOME Cybersecurity provides a flexible Software Development Kit (SDK) for connecting the PolarFire FPGA to the IoT By: Harry Ostaffe Vice President, Marketing @ Veridify…

RISC-V Forum Shenzhen: Unleashing Power of Electronics Making to Lead Global Open-Source Innovations

RISC-V Forum Shenzhen: Unleashing Power of Electronics Making to Lead Global Open-Source InnovationsOn October 17, the inaugural RISC-V Eco-system Development Forum, held as part of the Guangdong-Hong Kong-Macao Greater Bay Area Semiconductor Industry Expo, took place at…