Building on a Legacy of Security: Introducing Polar-VPX

Building on a Legacy of Security: Introducing Polar-VPXSundanceDSP, a leading provider of high-performance FPGA-based solutions, is proud to announce the latest addition to its product lineup: Polar-VPX. This cutting-edge 3U VPX form-factor…

Soft Tiling RISC-V Processor Clusters Speed Design and Reduce Risk

Soft Tiling RISC-V Processor Clusters Speed Design and Reduce RiskBy John Min John Min is VP of Customer Success at Arteris. He possesses architectural expertise that enables the successful management of design trade-offs…

How NVIDIA Shipped One Billion RISC-V Cores In 2024

How NVIDIA Shipped One Billion RISC-V Cores In 2024At the recent RISC-V North America summit, NVIDIA’s Vice President of Multimedia Architecture, Frans Sijstermans gave his insight into why NVIDIA chose RISC-V as the…

RISC-V HPC excitement at Supercomputing 2024 sets up an unmissable ISC 2025

RISC-V HPC excitement at Supercomputing 2024 sets up an unmissable ISC 2025By: Nick Brown, EPCC High Performance Computing (HPC) is one of the most exciting and challenging fields, solving the world's biggest problems with incredible levels…

RISC-V at Embedded World 2025: Innovation, Networking & Must-See Sessions

RISC-V at Embedded World 2025: Innovation, Networking & Must-See SessionsThe RISC-V Pavilion returns to embedded world for 2025! Visit us in Hall 5, Stand 5-119, to discover the latest RISC-V technologies and applications and…

TestRIG – Randomized Testing of RISC-V CPUs

TestRIG – Randomized Testing of RISC-V CPUsTestRIG (Testing with Random Instruction Generation) is a testing framework for RISC-V implementations. The RISC-V community has standardized a formal model of the architecture in…

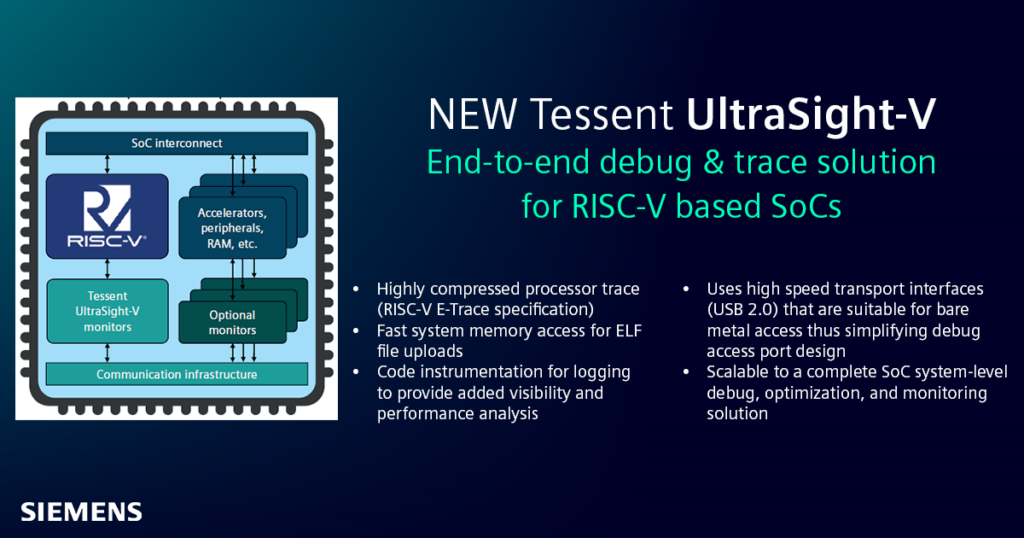

Accelerating RISC-V development with Tessent UltraSight-V

Accelerating RISC-V development with Tessent UltraSight-VBy: Francisca Tan, Product Management Lead – Tessent Embedded Analytics Siemens’ longstanding and deep engagement with the RISC-V community dates back to the foundation’s early…

Towards an Integrated Matrix Extension: Workload Analysis of CNN Inference with QEMU TCG Plugings

Towards an Integrated Matrix Extension: Workload Analysis of CNN Inference with QEMU TCG PlugingsIntroduction Following the gap analysis done in the second half of 2023, the Vector Special Interest Group (SIG-Vector) has been working on specifying instructions to…

RISC-V launches search for new CEO

RISC-V launches search for new CEO2024 was a year of accelerating momentum for RISC-V. Adoption grew across a diverse range of markets, the foundational new RVA23 Profile was ratified, and many new…

Chromium Performance Optimization on XuanTie RISC-V Processors

Chromium Performance Optimization on XuanTie RISC-V ProcessorsYang Li, Alibaba DAMO Academy Chromium, the most widely adopted open-source browser engine, serves as the foundation for numerous mainstream applications, including Chrome, Electron, VSCode,…

RISC-V International Newsletter – December 2024

RISC-V International Newsletter – December 2024Message from RISC-V International As we reflect on 2024, we wanted to express our heartfelt gratitude to the entire RISC-V ecosystem. This year has been…

Exploring RISC-V ISA Developments and Technical Highlights from 2024

Exploring RISC-V ISA Developments and Technical Highlights from 20242024 has been a year of great technical progress for the RISC-V ISA. Our 75 Committees and Groups, staffed by contributors from RISC-V member organizations…

RISC-V sees widespread commercial adoption across industries, from embedded to AI, from IoT to HPC and beyond Zurich – Dec. 8, 2020 – RISC-V International,…

RISC-V International Announces Agenda for the Third Annual RISC-V Summit

RISC-V International Announces Agenda for the Third Annual RISC-V SummitThe leading RISC-V conference will be held virtually this year, featuring keynotes, tutorials, exhibitions, networking opportunities and more WHAT: The RISC-V International Association has announced…

The schedule for RISC-V Global Forum is live! We have an exciting lineup of keynotes, session presentations, lightning talks, ask the experts, sponsor exhibits, and…

It is hard to believe, but the RISC-V project is ten years old today! RISC-V at HotChips, Flint Center, Cupertino CA, August 2014 After careful…

The DC-ROMA Laptop II has undergone comprehensive upgrades in both hardware and software, offering enhanced computing power and energy efficiency, as well as extensive system…

Exploring the RISC-V Summit 2024: Technical Sessions Announced

Exploring the RISC-V Summit 2024: Technical Sessions AnnouncedThe RISC-V Summit North America Plenary Sessions are now live on the event website. Each year, we are continually impressed with the high caliber of…

Trailblazers: Board of Directors Technical Award Winners 2024

Trailblazers: Board of Directors Technical Award Winners 2024By: Iris Zheng, Digital Marketing Intern, RISC-V International Five technical leaders were honored at RISC-V Summit Europe 2024 for their remarkable contributions to the RISC-V…

SpacemiT Key Stone K1 AI CPU has been adapted to the Fedora operating system successfully. With the Fedora operating system successfully running on the MUSE…

More than 1,300 Attendees Expected at RISC-V Summit China Next Week

More than 1,300 Attendees Expected at RISC-V Summit China Next WeekCheck out all the impressive talks and co-located events Next week, from August 21-23, more than 1,300 attendees will gather at the Huanglong Hotel in…

Microchip, and O.C.E. Technology deliver high-reliability RTOS for Polarfire® SoC FPGA space applications

Microchip, and O.C.E. Technology deliver high-reliability RTOS for Polarfire® SoC FPGA space applicationsBy: Barry Kavanagh, Chief Executive Officer, O.C.E. Technology Ltd. Polarfire® SoC FPGA RISC-V space applications can now take advantage of an RTOS compliant to ESA…

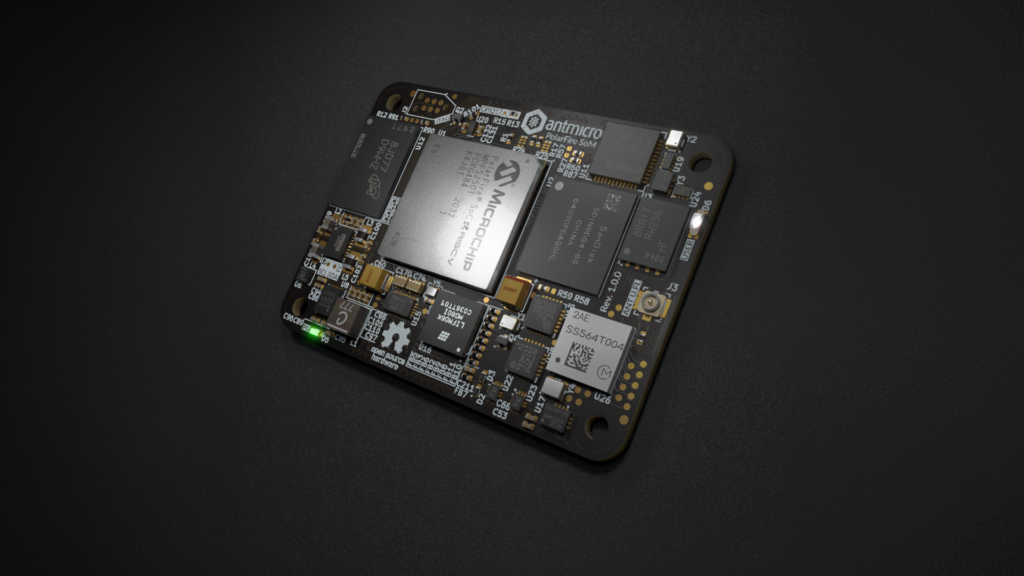

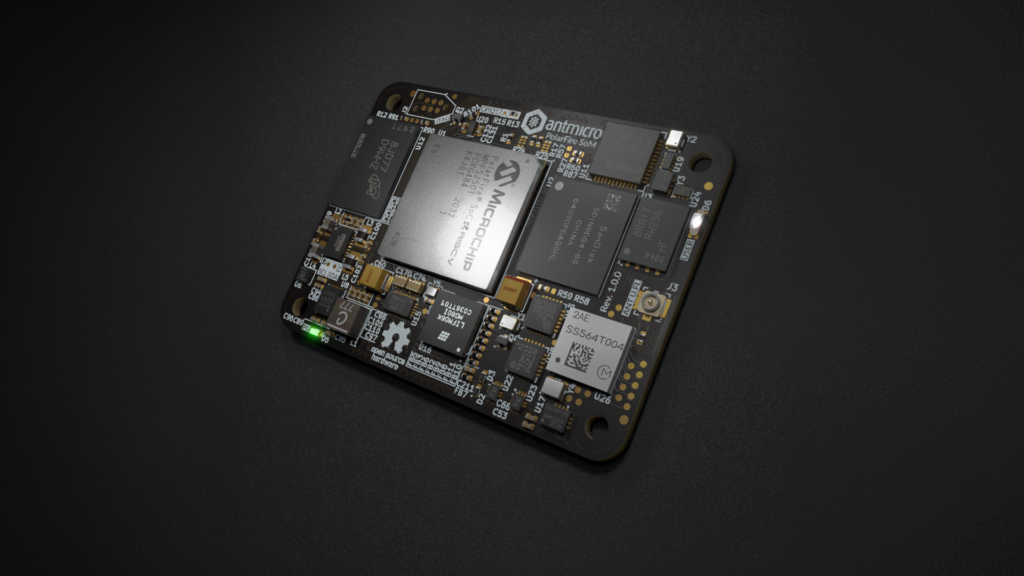

Open source System on Module with Microchip PolarFire SoC

Open source System on Module with Microchip PolarFire SoCThe PolarFire SoC was the world’s first Linux-enabled mass market multi-core RISC-V SoC, originally made available pre-silicon by Microchip through Antmicro’s Renode simulation framework. Thanks…

By: Antmicro The openness and customizability of the RISC-V ISA has encouraged its use across a variety of scenarios, such as supporting cores in larger…

Debugging of RISC-V-Based Chips Made Easy

Debugging of RISC-V-Based Chips Made EasyFROM SIMPLE MICROCONTROLLERS TO COMPLEX MULTICORE SOCS RISC-V cores can be found in increasingly more chips, either as the main CPU(s) or as a companion…

New Launch: Advanced RISC-V Courses | Maven Silicon

New Launch: Advanced RISC-V Courses | Maven SiliconBy: Maven Silicon We are delighted to inform you that we have recently published Advanced RISC-V Processor IP Design and Verification Online Courses. Our Founder and…

With Innovative technology, a collaborative spirit and a unique value proposition, Chip flow is setting itself to be the next generation of semiconductor solutions. Interview…

RT-Thread: Pioneering Real-Time Operating System for RISC-V

RT-Thread: Pioneering Real-Time Operating System for RISC-VIn the realm of modern computing architectures, the emergence of RISC-V marks a significant development, offering unprecedented openness and flexibility for processor design and implementation.…

The DC-ROMA Laptop II has undergone comprehensive upgrades in both hardware and software, offering enhanced computing power and energy efficiency, as well as extensive system…

Exploring the RISC-V Summit 2024: Technical Sessions Announced

Exploring the RISC-V Summit 2024: Technical Sessions AnnouncedThe RISC-V Summit North America Plenary Sessions are now live on the event website. Each year, we are continually impressed with the high caliber of…

Trailblazers: Board of Directors Technical Award Winners 2024

Trailblazers: Board of Directors Technical Award Winners 2024By: Iris Zheng, Digital Marketing Intern, RISC-V International Five technical leaders were honored at RISC-V Summit Europe 2024 for their remarkable contributions to the RISC-V…

SpacemiT Key Stone K1 AI CPU has been adapted to the Fedora operating system successfully. With the Fedora operating system successfully running on the MUSE…

More than 1,300 Attendees Expected at RISC-V Summit China Next Week

More than 1,300 Attendees Expected at RISC-V Summit China Next WeekCheck out all the impressive talks and co-located events Next week, from August 21-23, more than 1,300 attendees will gather at the Huanglong Hotel in…

Microchip, and O.C.E. Technology deliver high-reliability RTOS for Polarfire® SoC FPGA space applications

Microchip, and O.C.E. Technology deliver high-reliability RTOS for Polarfire® SoC FPGA space applicationsBy: Barry Kavanagh, Chief Executive Officer, O.C.E. Technology Ltd. Polarfire® SoC FPGA RISC-V space applications can now take advantage of an RTOS compliant to ESA…

Open source System on Module with Microchip PolarFire SoC

Open source System on Module with Microchip PolarFire SoCThe PolarFire SoC was the world’s first Linux-enabled mass market multi-core RISC-V SoC, originally made available pre-silicon by Microchip through Antmicro’s Renode simulation framework. Thanks…

By: Antmicro The openness and customizability of the RISC-V ISA has encouraged its use across a variety of scenarios, such as supporting cores in larger…

Debugging of RISC-V-Based Chips Made Easy

Debugging of RISC-V-Based Chips Made EasyFROM SIMPLE MICROCONTROLLERS TO COMPLEX MULTICORE SOCS RISC-V cores can be found in increasingly more chips, either as the main CPU(s) or as a companion…

New Launch: Advanced RISC-V Courses | Maven Silicon

New Launch: Advanced RISC-V Courses | Maven SiliconBy: Maven Silicon We are delighted to inform you that we have recently published Advanced RISC-V Processor IP Design and Verification Online Courses. Our Founder and…

With Innovative technology, a collaborative spirit and a unique value proposition, Chip flow is setting itself to be the next generation of semiconductor solutions. Interview…

RT-Thread: Pioneering Real-Time Operating System for RISC-V

RT-Thread: Pioneering Real-Time Operating System for RISC-VIn the realm of modern computing architectures, the emergence of RISC-V marks a significant development, offering unprecedented openness and flexibility for processor design and implementation.…