Porting and Optimizing Android ART on XuanTie C910

Porting and Optimizing Android ART on XuanTie C910By Lifang Xia Over the past three years, our team has undertaken the substantial task of porting Android 10 and Android 12 to the XuanTie…

Developing and testing heterogeneous space-grade systems with Renode

Developing and testing heterogeneous space-grade systems with RenodeWhile landing humans on the Moon was a feat accomplished with very basic compute power of 2MHz provided by the Apollo Guidance Computer, modern spacecraft…

Announcing The Fourth International Workshop on RISC-V for HPC

Announcing The Fourth International Workshop on RISC-V for HPCThe RISC-V HPC Special Interest Group is organising a workshop at ISC24, one of the leading High Performance Computing (HPC) conferences. The workshop will run…

Integrating ROS 2 With Microchip’s PolarFire® SoC FPGA

Integrating ROS 2 With Microchip’s PolarFire® SoC FPGAROS (Robot Operating System) is a popular open-source framework used for creating robotics applications. It provides a set of tools and libraries for building complex…

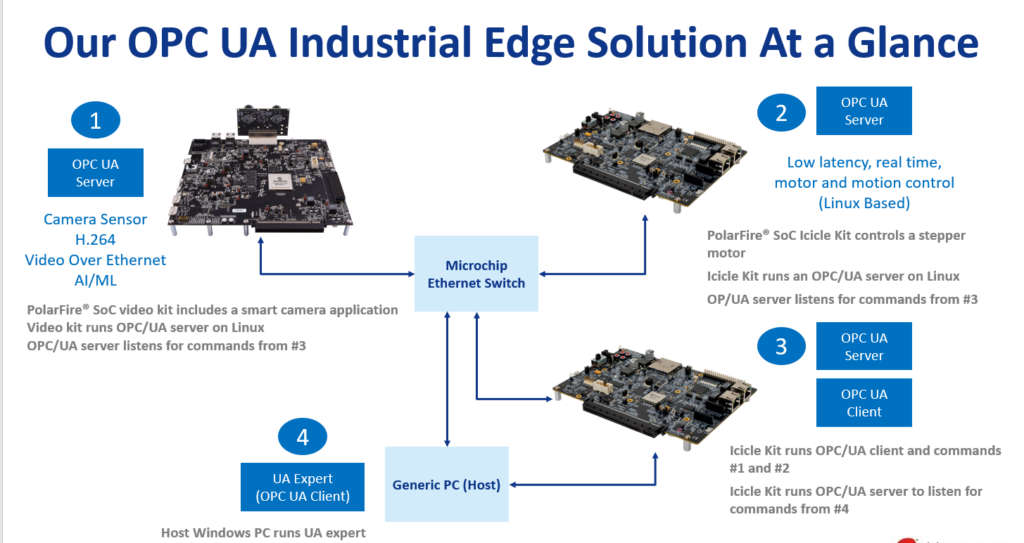

OPC UA on PolarFire SoC: Enabling Industrial Edge Solutions

OPC UA on PolarFire SoC: Enabling Industrial Edge SolutionsWebpage: https://www.microchip.com/en-us/solutions/industrial/fpga/opc-ua Author: Apurva Peri, Principal Engineer, FPGA Product Marketing The Modern Industrial Edge The Industrial Edge has become the standard for industrial automation requirements,…

Author- Rich Wawrzyniak Principal Analyst at The SHD Group As we start 2024, The SHD Group has released a comprehensive market analysis report titled "RISC-V…

Expanding RISC-V support in Renode with Bit-Manipulation extensions

Expanding RISC-V support in Renode with Bit-Manipulation extensionsAntmicro’s open source Renode simulation framework offers support for various instruction set architectures, with the RISC-V ISA being a major focus for – as a…

Message from RISC-V International As we look back on 2023, we wanted to express our gratitude to the entire RISC-V ecosystem. Throughout the year, we…

Five years of SERVing

Five years of SERVingAuthor: Olof Kindgren Making your own RISC-V CPU is a terrible idea. I have said that many times before. There are already a million RISC-V…

The Top 10 RISC-V Milestones & Highlights from 2023

The Top 10 RISC-V Milestones & Highlights from 2023Looking back at 2023, there are many different ways to measure progress and success. You could point to the growing adoption of RISC-V—which is in…

Developing and testing with Renode in heterogeneous, multi-node automotive use cases

Developing and testing with Renode in heterogeneous, multi-node automotive use casesAutomotive engineering in the past 30 years has been transformed by the growing capabilities of microprocessors, enabling their use in a wide range of the…

NOEL-V: A RISC-V Processor for High-Performance Space Applications

NOEL-V: A RISC-V Processor for High-Performance Space ApplicationsSpace applications pose significant challenges for electronic systems as they must contend with a myriad of environmental factors once they are launched. These factors include…

RISC-V: An Open Standard Instruction Set Architecture

RISC-V: An Open Standard Instruction Set ArchitectureBy Mark Himelstein, CTO of RISC-V International In this blog post, we’ll explain why RISC-V is an open standard instruction set architecture (ISA). We’ve received…

RISC-V Announces Agenda for 2023 RISC-V Summit Europe

RISC-V Announces Agenda for 2023 RISC-V Summit EuropeThe first-ever RISC-V Summit Europe includes keynotes, technical talks, working groups, poster sessions, networking opportunities, and more RISC-V International will host its first annual…

By: Charlie Cheng, Managing Director of Polyhedron LLC Andes Technology Corp. was founded in 2004 and is headquartered in Taiwan, with a significant presence in…

Kenning helps develop real-world Machine Learning solutions for ARM and RISC-V platforms such as NVIDIA Jetson AGX Orin, Google Coral or HiFive Unmatched by seamlessly…

T-Head Prototypes Innovative Hardware Support for Virtual IOMMU

T-Head Prototypes Innovative Hardware Support for Virtual IOMMUAuthor: Chong Ren Recently, T-Head has completed the QEMU-based proof-of-concept of hardware support for virtual IOMMU for virtual machines, based on the specification in the…

[INTERVIEW] Calista Redmond, RISC-V International | Open Source Summit NA 2023

[INTERVIEW] Calista Redmond, RISC-V International | Open Source Summit NA 2023Calista Redmond talks with John Furrier & Rob Strechay at Open Source Summit NA 2023 in Vancouver, Canada.

The RISC-V Golden model, also called the Sail model, defines the instruction execution of the RISC-V architecture. As such, it is useful for evaluating the…

Chip War Without Soldiers

Chip War Without SoldiersAuthor: P R Sivakumar, Founder and CEO, Maven Silicon LinkedIn Profile: https://www.linkedin.com/in/sivapr/ Every country realizes the importance of producing skilled chip designers who could decide…

[WEBINAR] Taking the Risk out of Developing Your Own RISC-V Processor with Fast, Architecture-Driven, PPA Optimization

[WEBINAR] Taking the Risk out of Developing Your Own RISC-V Processor with Fast, Architecture-Driven, PPA OptimizationAre you developing or thinking about developing your own RISC-V processor? You’re not alone. The use of the RISC-V ISA to develop processors for SoCs…

May 10, 2023: Canonical published the optimised Ubuntu release for StarFive’s VisionFive 2, the world’s first high-performance RISC-V single board computer (SBC) with an integrated…

Wearable Payment Solution Based On T-Head Security Technologies

Wearable Payment Solution Based On T-Head Security TechnologiesBy Xiaoxia Cui Wearable devices, such as smartwatches and pulse oximeters, are gaining popularity with the continuous expansion of IoT applications in recent years. However,…

NOEL-V: A RISC-V Processor for High-Performance Space Applications

NOEL-V: A RISC-V Processor for High-Performance Space ApplicationsSpace applications pose significant challenges for electronic systems as they must contend with a myriad of environmental factors once they are launched. These factors include…

RISC-V: An Open Standard Instruction Set Architecture

RISC-V: An Open Standard Instruction Set ArchitectureBy Mark Himelstein, CTO of RISC-V International In this blog post, we’ll explain why RISC-V is an open standard instruction set architecture (ISA). We’ve received…

RISC-V Announces Agenda for 2023 RISC-V Summit Europe

RISC-V Announces Agenda for 2023 RISC-V Summit EuropeThe first-ever RISC-V Summit Europe includes keynotes, technical talks, working groups, poster sessions, networking opportunities, and more RISC-V International will host its first annual…

By: Charlie Cheng, Managing Director of Polyhedron LLC Andes Technology Corp. was founded in 2004 and is headquartered in Taiwan, with a significant presence in…

Kenning helps develop real-world Machine Learning solutions for ARM and RISC-V platforms such as NVIDIA Jetson AGX Orin, Google Coral or HiFive Unmatched by seamlessly…

T-Head Prototypes Innovative Hardware Support for Virtual IOMMU

T-Head Prototypes Innovative Hardware Support for Virtual IOMMUAuthor: Chong Ren Recently, T-Head has completed the QEMU-based proof-of-concept of hardware support for virtual IOMMU for virtual machines, based on the specification in the…

[INTERVIEW] Calista Redmond, RISC-V International | Open Source Summit NA 2023

[INTERVIEW] Calista Redmond, RISC-V International | Open Source Summit NA 2023Calista Redmond talks with John Furrier & Rob Strechay at Open Source Summit NA 2023 in Vancouver, Canada.

The RISC-V Golden model, also called the Sail model, defines the instruction execution of the RISC-V architecture. As such, it is useful for evaluating the…

Chip War Without Soldiers

Chip War Without SoldiersAuthor: P R Sivakumar, Founder and CEO, Maven Silicon LinkedIn Profile: https://www.linkedin.com/in/sivapr/ Every country realizes the importance of producing skilled chip designers who could decide…

[WEBINAR] Taking the Risk out of Developing Your Own RISC-V Processor with Fast, Architecture-Driven, PPA Optimization

[WEBINAR] Taking the Risk out of Developing Your Own RISC-V Processor with Fast, Architecture-Driven, PPA OptimizationAre you developing or thinking about developing your own RISC-V processor? You’re not alone. The use of the RISC-V ISA to develop processors for SoCs…

May 10, 2023: Canonical published the optimised Ubuntu release for StarFive’s VisionFive 2, the world’s first high-performance RISC-V single board computer (SBC) with an integrated…

Wearable Payment Solution Based On T-Head Security Technologies

Wearable Payment Solution Based On T-Head Security TechnologiesBy Xiaoxia Cui Wearable devices, such as smartwatches and pulse oximeters, are gaining popularity with the continuous expansion of IoT applications in recent years. However,…