Stay Connected With RISC-V

We send occasional news about RISC-V technical progress, news, and events.

The RISC-V Exchange hosts the hardware, software, services, and learning offerings in the RISC-V community. Browse the list or search for an offering below.

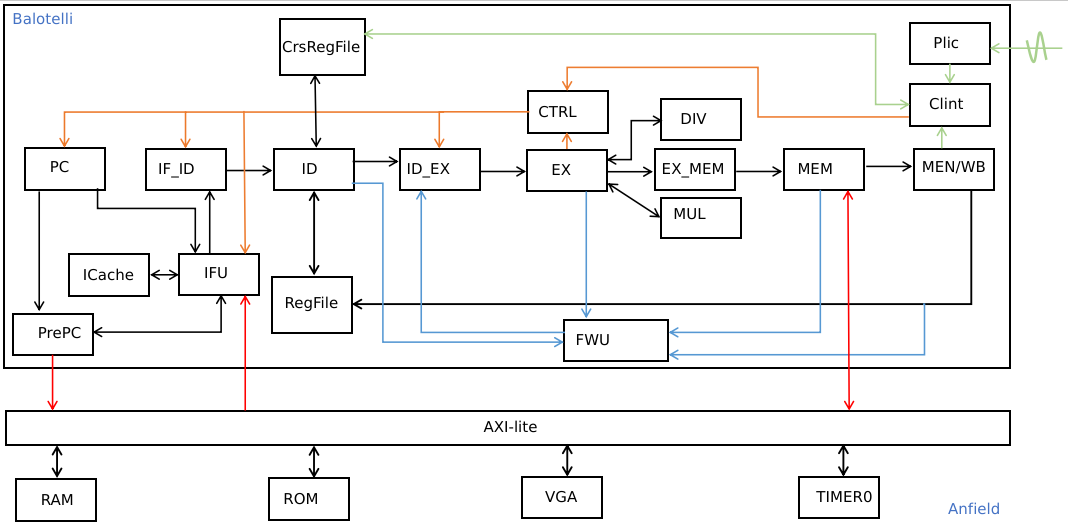

Organization: Kai

An incomplete SoC

Software Type: Soft IP

Organization: Digital Core Design

DCD’s RV32IMZicsr RISC-V Core The DRV32IMZicsr is a 32-bit RISC-V CPU with M, Zicsr extensions, and External Debug support. The Core belongs to the latest DCD’s DRVX Core Family, with: a five-stage pipeline, Harvard architecture flexible size of program and data memory together with their allocation in address space. It is possible to select CPU interface as: AXI, AHB, Native. The DRV32IMZicsr was developed as ISO26262 Safety Element out of Context (SEooC) and is technology independent, and compatible with all FPGA and ASIC vendors. The DRV32IMZicsr can be used along with a wide range of DCD’s peripherals, like e.g. DMA, SPI, UART, PWM, CAN etc. This holistic approach makes the DRV32IMZicsr core a good choice for application for e.g. Automotive, Internet of Things, Embedded, Consumer Electronics, and more. The DRV32IMZicsr is a 32-bit core with 32 General Purpose Registers. It performs arithmetic and logic instructions, loads, stores, conditional branches, and unconditional jumps. The proper usage of base instructions provides an additional set of pseudo instructions which are available in the RISC-V assembly language. The M extension enables the use of additional integer multiplication and division instructions due to Multiplication and Division unit, which is responsible for handling these instructions. The Zicsr extension provides the means to access Control and Status Registers, which in turn enables interrupt and exception handling according to version 20211203 of The RISC-V Instruction Set Manual Volume II: Privileged Architecture. With Zicsr extension DRV32IMZicsr core is also equipped with performance counters and timers. External Debug support utilizes JTAG debug interface and is implemented with conformance to the RISC-V Debug Specification 0.13.2 and 1.0.0. That allows core debugging with all the tools compatible with this specification available on the market. The DRV32IMZicsr core is delivered with a fully automated test bench and a complete set of tests, allowing easy package validation at each stage of the SoC design flow. DESIGN FEATURES: ALL DCD’S IP CORES ARE TECHNOLOGY INDEPENDENT WHICH MEANS THAT THEY ARE 100% COMPATIBLE WITH ALL FPGA & ASIC VENDORS E.G. Altera / Intel, Xilinx / AMD, Lattice, Microsemi / Microchip, and others. TSMC UMC SK Hynix and others.

Software Type: Soft IP

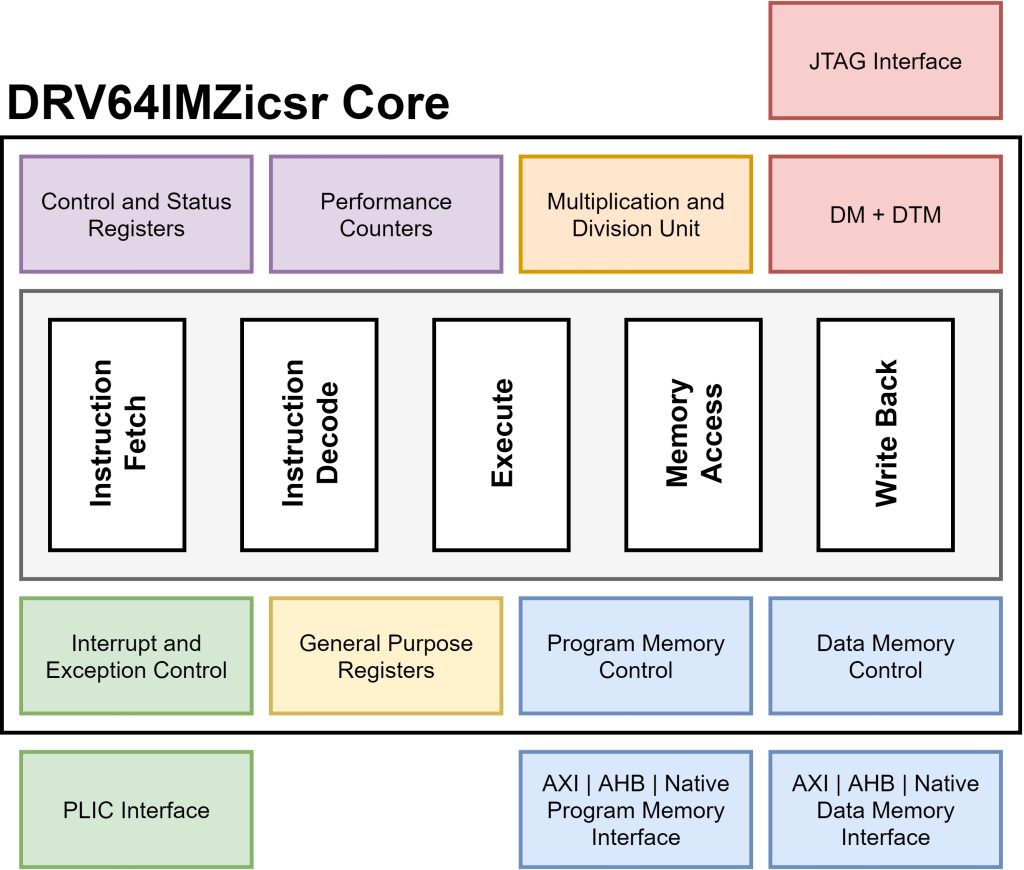

Organization: Digital Core Design

The DRV64IMZicsr is a 64-bit RISC-V CPU with M, Zicsr extensions and External Debug support. As a part of the DRVX Core Family this unique CPU offers: five-stage pipeline, Harvard architecture, flexible size of program and data memory together with their allocation in address space. To give you freedom of choice, you can easily select the CPU interface: AXI, AHB Native. The DRV64IMZicsr was developed as ISO26262 Safety Element out of Context (SEooC) and is technology independent, and compatible with all FPGA and ASIC vendors. As we believe in DCD that one CPU is not enough… you can easily use it with a wide range of DCD’s peripherals, including DMA, SPI, UART, PWM, CAN, and more. These unique features make DRV64IMZicsr core a good choice for many applications like e.g. Automotive, Internet of Things, Embedded, Consumer Electronics and many more. The DRV64IMZicsr is 64-bit core with 32 General Purpose Registers. It performs arithmetic and logic instructions, loads, stores, conditional branches, and unconditional jumps. What’s more, proper usage of base instructions provides an additional set of pseudo instructions which are available in the RISC-V assembly language. The M extension enables the usage of additional integer multiplication and division instructions due to Multiplication and Division unit which is responsible for handling these instructions. The Zicsr extension provides the means to access Control and Status Registers which in turn enables interrupt and exception handling according to version 20211203 of The RISC-V Instruction Set Manual Volume II: Privileged Architecture. With Zicsr extension DRV64IMZicsr core is also equipped with performance counters and timers. External Debug support utilizes JTAG debug interface and is implemented with conformance to the RISC-V Debug Specification 0.13.2 and 1.0.0. That allows core debugging with all tools compatible with this specification available on the market. The DRV64IMZicsr core is delivered with fully automated test bench and a complete set of tests, allowing easy package validation at each stage of the SoC design flow.

License Type: Copyleft

Software Type: Soft IP

Software Type:

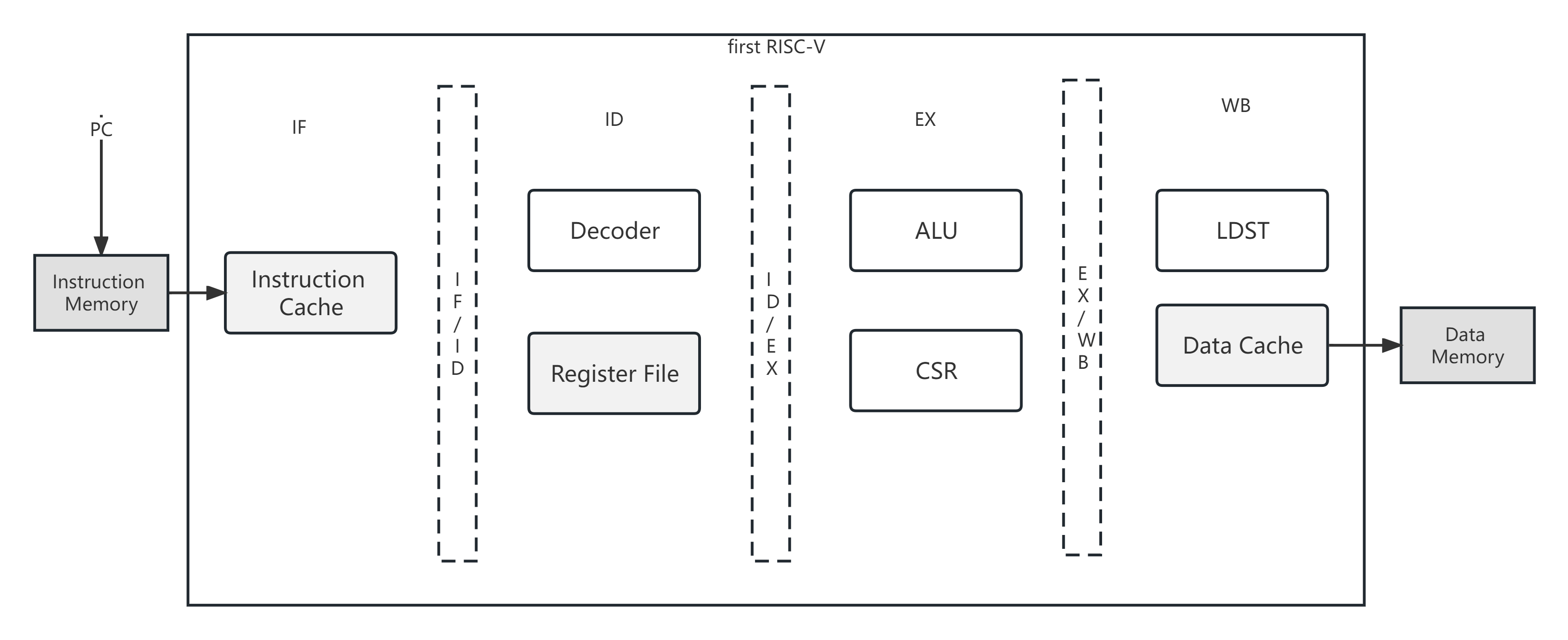

Organization: OpenHDL

A Harvard architecture CPU based on RISC-V.

License Type: GPL

Software Type: Chips

Try to implement a RISC-V CPU for studying RISC-V ISA by Amarath(Python-style) language

License Type: Copyleft

Software Type: Chips

Organization: Indian Institute of Science, Bangalore

32-bit, 5-Stage Pipelined RISC-V Core

License Type: Proprietary

Software Type: Soft IP

Organization: Indian Institue of Science, Bangalore

32-bit, 5 Stage Pipelined RISC-V Core with Vector Extension Support

License Type: Proprietary

Software Type: Soft IP

Organization: Indian Institute of Science, Bangalore

64-bit, 4-wide issue, Out-of-Order RISC-V Processor

License Type: Proprietary

Software Type: Soft IP

Software Type:

Organization: Imagination Technologies

A RISC-V application processor with compelling performance density, seamless security and the artificial intelligence capabilities needed to support the compute and intuitive user experience needs for next generation consumer and industrial devices.

License Type: Proprietary

Software Type: Soft IP

Software Type:

Organization: Imagination Technologies

IMG RTXM-2200 is a highly scalable real-time, deterministic, 32-bit embedded CPU that is feature-rich and flexible in design for mainstream devices. It’s the ideal solution for markets such as cellular base stations, networking solutions for data transfer, packet management and storage controllers. It can also be used as a helper core in complex SoCs.

License Type: Proprietary

Software Type: Soft IP

Software Type:

We send occasional news about RISC-V technical progress, news, and events.