The De-RISC Project celebrates its second year through the introduction of a market-ready hardware-software platform based on the RISC-V instruction set architecture (ISA), productizing a multi-core RISC-V system-on-chip and an efficient time and space partitioning hypervisor.

Valencia, October 18th 2021 – After two years of execution, the international team of researchers from the De-RISC project continue developing the first RISC-V fully European platform for aerospace.

“I am proud of the great achievements that the De-RISC team have reached in these two years,” Paco Gómez-Molinero, coordinator of the project, said. “With hard work and enthusiasm, we managed to achieve the major project goals, and the team is highly motivated to continue with the positive development effort of the project”.

This H2020 project started in October 2019 and continues paving its way after two years of intense work which will run until September 2022. Throughout the project’s second year, the four members of the consortium have been able to progress not only in different hardware and software developments, but also in the validation strategy which will cover the different tests required to ensure that the system adheres to specification.

Hardware development

Throughout the project’s second year, the hardware component has been one of the main focus for the consortium and, more specifically for Cobham Gaisler and Barcelona Supercomputing Center (BSC). The consortium has released as open source the NOEL-V RISC-V processor model extensions, notably the H extensions (https://www.gaisler.com/getgrlib) supporting full virtualization. Additionally, the work carried out has also delivered good results in the statistics unit for multicore interference, which has been matured and released as open source (https://gitlab.bsc.es/caos_hw/hdl_ip/bsc_pmu/) as well.

Software development

On the software side, the consortium is progressing in the use cases area through the development of benchmarks, the on-board satellite software stack -which will use the LVCUGEN framework by CNES– and the Command and Data-Handling use-cases. Furthermore, the port of the hyperspectral image compression algorithm on the RISC-V platform is ongoing and it is expected to deliver results in the following months.

Validation development

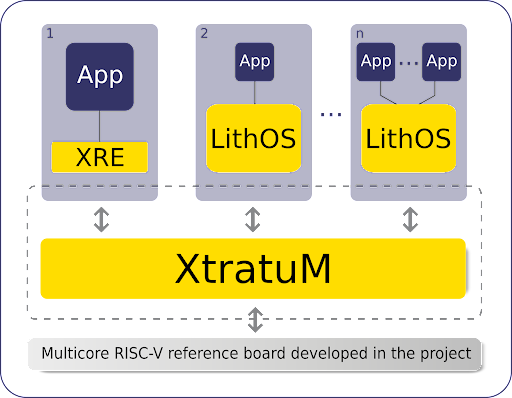

Regarding the validation work carried out in this second year, the consortium has defined the three use cases which will be executed in the project and which will have a very relevant role in the following months: an execution of low-level benchmarks, an on-board satellite software stack, and a Command & Data Handling subsystem. The members of the team have been preparing the validation environment of XtratuM Next Generation (XNG) and LithOS, and specified the software validation plan of the hypervisor and the end-user validation strategy. The advances in this work package are taking a main impact in the current development of the research project and the team is already developing and running the software stress tests as part of the performance validation of the multicore platform.

Future actions

In the following months, the De-RISC consortium will guarantee the correct progress of the project and will achieve the great majority of its results through the hard work and commitment that characterizes this group of researchers. The validation activities will be one of the main focus of the project and the hardware and software tasks will proceed as expected to support the use cases.

The evolution of De-RISC has been formidable in this period, following the steps of the first year. The participation in events, the good engagement in social media, and the presentation of the project to key stakeholders has led to a gaining popularity of the project in the aerospace domain. The future outlook for De-RISC seems promising and its final results will have a huge potential in the aerospace domain in the supply of a fully European Integrated Modular Avionics HW and SW platform.

Learn more in https://derisc-project.eu/

About De-RISC

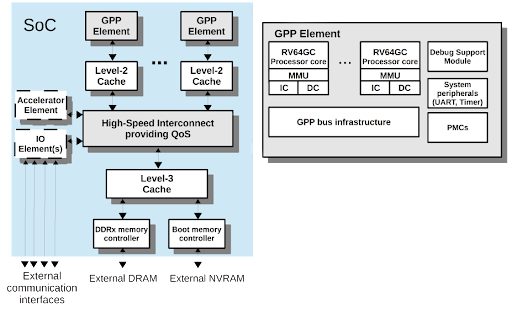

De-RISC (Dependable Real-time Infrastructure for Safety-critical Computer) is an Innovation Action partially funded by the European Commission, which was launched in October 2019. With a budget of € 3,444,625, the project addresses computer systems in the aerospace domain. It will introduce a market-ready hardware-software platform based on the RISC-V instruction set architecture (ISA), productizing a multi-core RISC-V system-on-chip designed by Cobham Gaisler and an efficient time and space partitioning based on the fentISS’ XtratuM hypervisor.

The project consortium comprises four partners who have extensive experience in the safety-critical and aerospace domains. The XtratuM hypervisor by fentISS (Spain) has been selected for different space missions including the OneWeb satellite constellation, the PLATiNO generic satellite for constellations, and ARGOS-NEO ANGELS, EyeSat, SVOM, JUICE and MMX among others. The microprocessors developed by Cobham Gaisler have been used in a variety of ESA and NASA missions. Barcelona Supercomputing Center is one of the leading research institutions in Europe and has closely collaborated with Gaisler and Thales in European projects such as SAFURE and PROXIMA. Thales is a world leader for mission critical information systems with ample experience in the aerospace, telecommunications and security domains.

Watch the De-RISC official video.

For more information please contact Ana Rísquez Navarro at fentISS