Learn more about IP Core Generation workflow from MATLAB® R2022A release onwards for PolarFire® SoC FPGA and SmartFusion® 2 family of Microchip FPGAs.

Introducing IP Core Generation for PolarFire SoC and SmartFusion 2 FPGAs

We are pleased to introduce IP Core Generation workflow from MATLAB R2022A release onwards for PolarFire® System-on-Chip (SoC) Field-Programmable Gate Array (FPGA) and SmartFusion® 2 family of Microchip FPGAs.

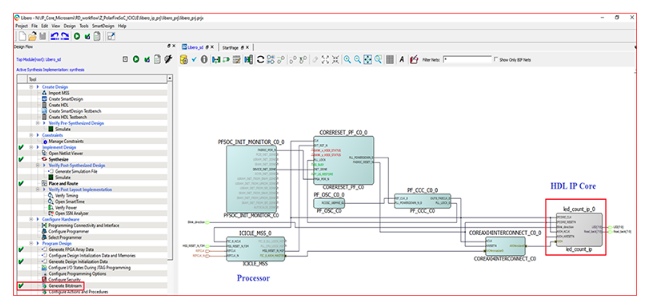

The integrated IP core generation workflow is compliant with the AXI4 interface supported by Libero SoC Design Suite; it also combines custom IP cores into Microchip SoC FPGAs with Libero SoC Sesign Suite tools. This workflow is being launched on PolarFire SoC Icicle Kit.

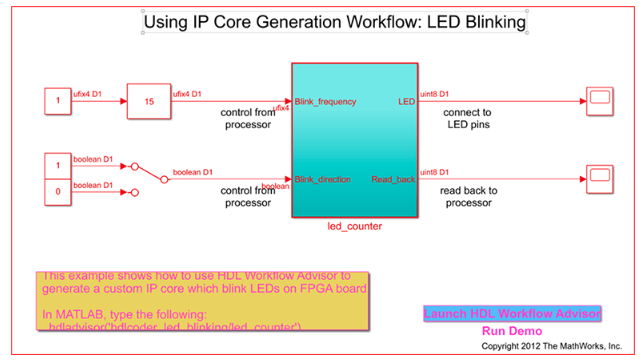

The IP core gen workflow is enabled by the HDL Coder support package. The algorithm I/Os are mapped to onboard interfaces through HDL Workflow Advisor (HDLWA). The HDLWA generates hardware description language (HDL) code, including VHSIC Hardware Description Language (VHDL) and Verilog. It also automatically synthesizes the HDL code and creates a bitstream file which can be deployed on a Microchip SoC FPGA. All of this is done with Libero SoC running in the backend.

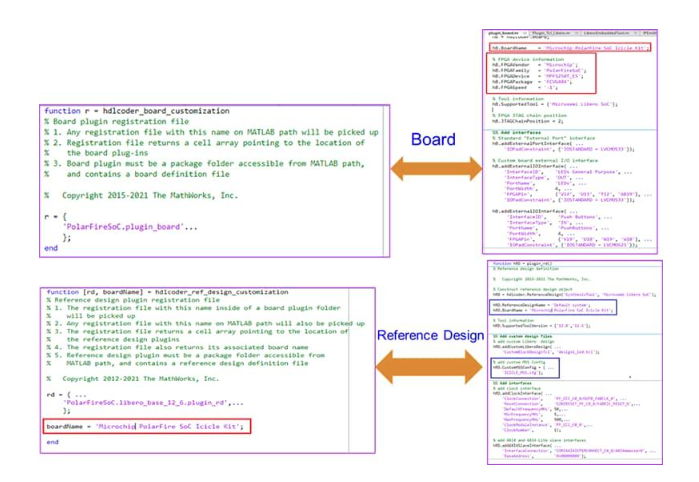

The Reference Design IP core gen workflow for Libero SoC Design Suite can be performed as follows:

- Create “Reference Design” from Libero SoC Design Suite Tool (Block Design)

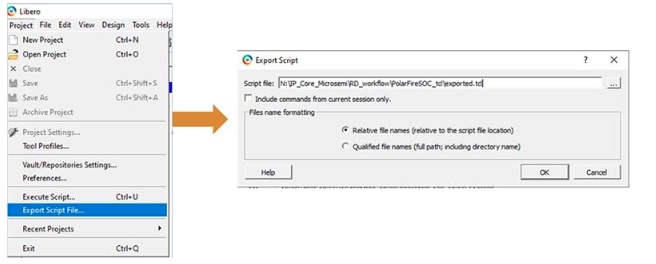

- Export the Reference Design to a TCL script

- Add necessary plugin files

- Create IP core from Simulink Model, insert in Reference Design, and Build FPGA Bitstream for Libero SoC Design Suite SmartDesign

- Integrated Design in Libero SoC with generated IP Core

To execute this workflow, customers will require the software tools mentioned below:

- Microchip (Libero SoC Design Suite v2022.1 onwards)

- Hardware Support Package for PolarFire SoC

- From within MATLAB Add On > “Get Hardware Support Package” option

- MathWorks Tools

Additionally, customers will require the following hardware:

- Microchip’s PolarFire SoC Icicle Kit Evaluation kit

- Microchip’s SmartFusion 2 system-on-chip (SoC) FPGA Advanced Development Kit

- Ethernet cable

- USB JTAG Cable – Programming the PolarFire Soc Icicle kit

The hardware support package automatically integrates our PolarFire SoC Icicle Kit and SmartFusion 2 system-on-chip (SoC) FPGA development kits.

Once the tools are installed, one needs to set up the Libero tool path in MATLAB by invoking the “hdlsetuptoolpath” command from the MATLAB prompt and setting the path to the Libero installer.

When you leverage MathWorks’ integrated IP Core generation workflow, enabled by our Accelerate Ecosystem, our FPGAs become ideal for a variety of applications within the industrial, defense and security markets, including motor control and digital signal processing, military communications, Smart Embedded Vision and control systems.

Want More?

For further information, please contact: miv@microchip.com