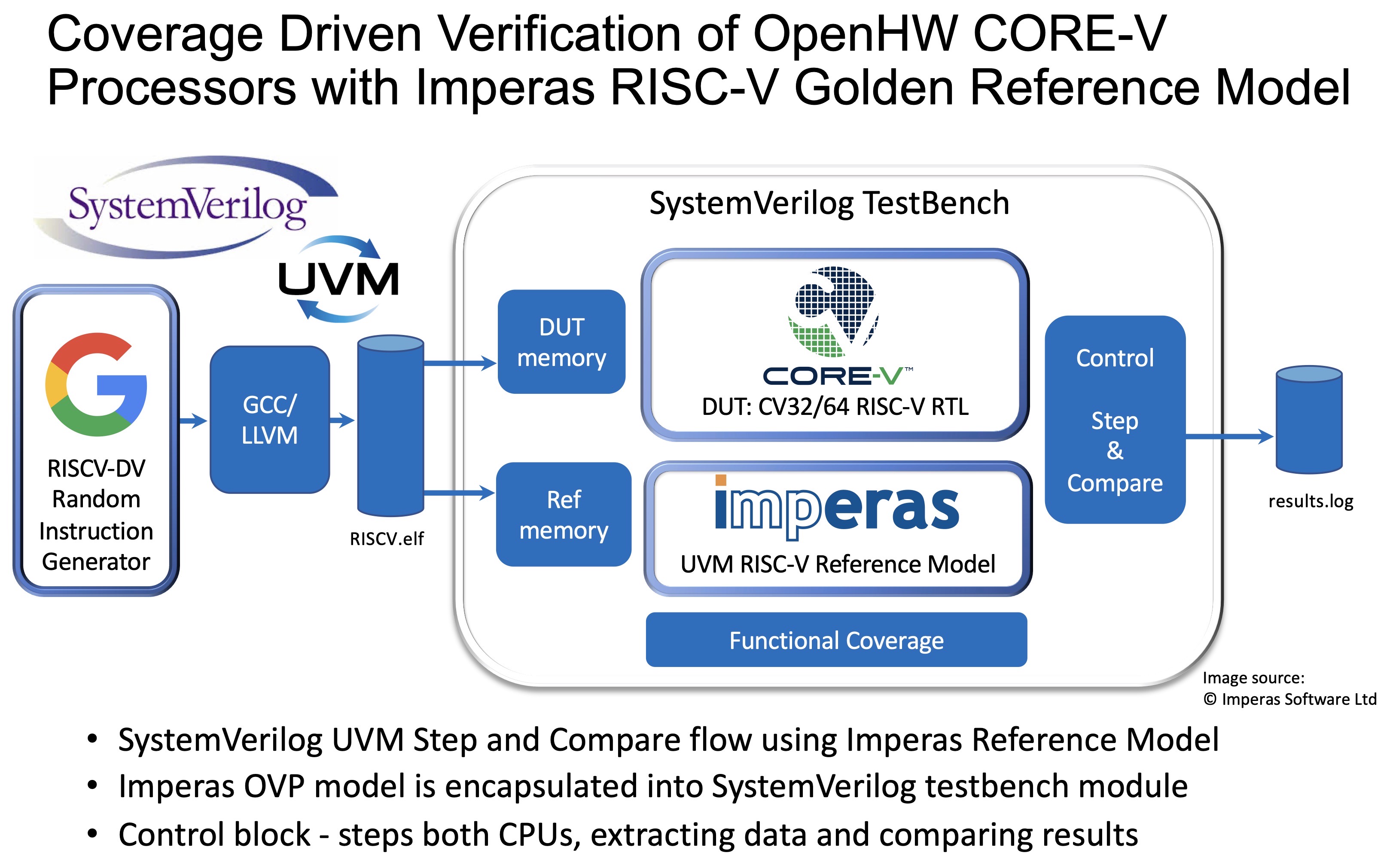

Oxford, United Kingdom, July 21st, 2020 — Imperas Software Ltd., the leader in virtual platforms and high-performance software simulation, today announced that OpenHW Group, the not-for-profit global organization set up to facilitate collaboration between hardware and software designers in the development of open-source IP, has established the CORE-V processor verification test bench using the Imperas RISC-V reference model to deliver quality IP cores to the OpenHW Group ecosystem and the open source hardware community. The OpenHW Group CORE-V Design Verification (DV) test plan is available at https://core-v-docs-verif-strat.readthedocs.io/en/latest/ together with the UVM testbench GitHub repository at https://github.com/openhwgroup/core-v-verif.

Article: https://www.imperas.com/articles/openhw-ecosystem-implements-imperas-risc-v-reference-models-coverage-driven-verification

Article: https://www.imperas.com/articles/openhw-ecosystem-implements-imperas-risc-v-reference-models-coverage-driven-verification

Stay Connected With RISC-V

We send occasional news about RISC-V technical progress, news, and events.

Copyright © 2023 RISC-V International®. All rights reserved. RISC-V, RISC-V International, and the RISC-V logos are trademarks of RISC-V International. For trademark usage guidelines, please see our Brand Guidelines and Privacy Policy